# **MONO: A sub-threshold microcontroller for** near-zero-power sensor applications

James Myers, ARM Resea

# Driving Applications: Near Zero Power RF and Sensor Operations (N-ZERO)

### The Challenge

DARPA's N-ZERO program poses the challenge to design always-on sensors and wakeup radios with 10nW power consumption. Very interesting prototype chips are now being demonstrated that meet the extremely difficult target and provide a smart wakeup source to a microcontroller (MCU).

For system designers seeking to make use of N-ZERO sensors, there is a stark choice to be made when it comes to selecting a commercial MCU. To use an easily programmable and performant 32b MCU with leakage power which swamps the new sensor? Or to use an 8b MCU with comparable leakage power but poor active power and performance?

| COTS MCU examples | SiLabs EFM32ZG108     | SiLabs C8051F91x    |

|-------------------|-----------------------|---------------------|

| Processor         | 32b ARM Cortex-M0+    | 8b 8051 compatible  |

| Shutdown Power    | 60nW                  | 10nW                |

| Active Power      | 2.7mA @ 24MHz         | 3.8mA @ 24MHz       |

| Peak Performance  | 21.6M 32b             | 3-25M 8b            |

|                   | instructions/second   | instructions/second |

|                   | (Dhrystone benchmark) | (peak, no branches) |

MONO seeks to plug this gap, marrying ultra low leakage with 32b performance and programmability at greater active power efficiency.

| Power  |        | CO<br>Rac    |         | Run MCU at sub-threshold to<br>achieve 10uW active power         |

|--------|--------|--------------|---------|------------------------------------------------------------------|

| 10ew   |        | MON0<br>MCU  | Active  | Power matched mixed-signal is key<br>to whole chip solution      |

| 10/W - | N-ZERO | Duty-cycling | Standby | Reduce standby power to 10nW while still preserving useful state |

| 20+W   | •      | •            |         | Aggressive system/circuit co-<br>optimization needed             |

What additional system functionality could this enable?

- Allow digital sensor fusion in addition to analog fusion Filter false alarms from 1/hour to 1/day or less, reducing radio

- activity and extending battery life Preserve some (judicious) sensor history and adapt to environment On real alarms, communicate historical context as well as immediate

- Provide periodic self-test to ensure node is operational

## **Project Outputs**

The MONO project intends to deliver an optimized MCU with HW/SW environment enabling government contractors to develop new applications and to have new chips fabricated for government use. For application-specific feasibility studies to be conducted in parallel to the MONO project, we will release regularly updated data sheets describing system performance, memory capacity, etc. Some specific outputs are:

- Projected data sheets towards the final system

- · Demo board and testchip implementing an example application

- Development board and infrastructure for new software development

- Chip generator to via-program ROMs with new software

The photo below shows the chip 1 test board, providing full testability of prototype circuits. Final demo and development boards are expected to be simpler

#### ROM for code, RAM for development

Non-volatile memories such as embedded flash have excellent flexibility but large power due to high voltage charge pumps and complex sensing schemes. MONO uses ROM as it is inherently more efficient and can also be designed to scale with logic to optimally efficient sub-threshold voltages

The drawback is that the code is fixed at manufacturing time. To enable development of new code, MONO includes a dense SRAM which can hold work-in-progress software while it is tested, debugged and verified. Once completed, a new chip layout can be generated (without the use of EDA tools), using a chip generator licensed from Arm.

#### **Specifications (Subject to Change)**

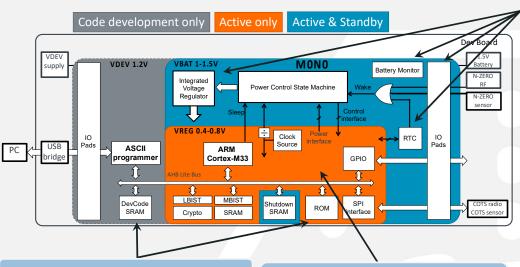

- Processor: Arm Cortex-M33 with DSP extensions (no FPU)

- Battery voltage: 1-1.5V primary alkaline

- Functional temperature range: 0-85C

- Shutdown power: 10nW at 25C (IVR disabled and 4KB retention in Shutdown SRAM)

- **ROM capacity: 128kB**

- RAM capacity: 16kB active + 4kB shutdown

- Shutdown RAM breakeven time: 1s for full 4kB transfer

- Interfaces: SPI with up to 3 chip selects or up to 5 GPIO Performance: 0.5-50MHz

- Active power: 10uW-2mW Under SW control slower is more efficient

| Month                            |        | Phase 1 |   |     |   |    |      |   |   |    |     |     | -     |     | Phase 2<br>14 15 16 17 18 19 20 21 22 23 2 |    |     |       |      |    |    |     |      |      |       | Phase 3 |    |    |    |    |  |  |

|----------------------------------|--------|---------|---|-----|---|----|------|---|---|----|-----|-----|-------|-----|--------------------------------------------|----|-----|-------|------|----|----|-----|------|------|-------|---------|----|----|----|----|--|--|

|                                  | 1      | 2       | 3 | 4   | 5 | 6  | 7    | 8 | 9 | 10 | 11  | 12  | 13    | 14  | 15                                         | 16 | 17  | 18    | 19   | 20 | 21 | 22  | 23   | 24   | 25    | 26      | 27 | 28 | 29 | 30 |  |  |

| Chip II (Tasks 1 + 2)            | Design |         |   | Fab |   |    | Test |   |   |    | L i | i I |       |     |                                            |    |     |       |      |    |    |     |      |      |       |         |    |    |    |    |  |  |

| Chip 2 + MOND Spec (Tasks 3 + 5) |        |         |   |     |   | De | sign |   |   |    | Fab |     | Test  |     |                                            |    |     |       |      |    |    |     |      |      |       |         |    |    |    |    |  |  |

| SW Report (Task 6)               |        |         |   |     |   |    |      |   |   |    | 2   | Dev | slapm | ent |                                            |    |     |       |      |    |    |     |      |      |       |         |    |    |    |    |  |  |

| Chip 3 (Tasks 4 + 8)             |        |         |   |     |   |    |      |   |   |    |     | De  | sign  |     |                                            |    | Fab |       | Test |    |    |     |      |      |       |         |    |    |    |    |  |  |

| Chip 4 (Tasks 7 + 9)             |        |         |   |     |   |    |      |   |   |    |     |     |       |     |                                            |    |     | Desig |      |    |    | Fab |      | Test |       |         |    |    |    |    |  |  |

| Demo Boards (Task 10)            |        |         |   |     |   |    |      |   |   |    | Ī   | i I |       |     |                                            |    |     |       |      |    |    | De  | sign |      | Board |         |    |    |    |    |  |  |

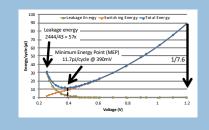

#### Sub-threshold operation for 10uW active power

Operating digital sub-systems below their threshold voltage has been shown in prior ARM work to increase energy efficiency by up to 10x. Once circuit challenges such as SRAM design and temperature variability are overcome, the next challenge is to deliver a range of performance/power points without undue burden to software.

MONO will remove the need for software to specify a regulator mode or voltage/frequency pair from a characterized lookup table - as is common for DVFS in mobile systems. The real requirement is for the hardware to deliver a guaranteed application-specific minimum performance. This can be done using our automatically scaling system clock source, as feedback to the voltage regulator. This also has the benefit of reduced regulator power in voltage comparators.

The figure below shows measured results from a first generation sub-threshold chip designed by Arm Research and published at ISSCC in 2015.

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions and/or findings expressed are those of the author and should not be interpreted as

representing the official views or policies of the Department of Defense or the U.S. Government.

Highly efficient integrated analog

for 10nW shutdown

The 10nW shutdown power budget for the chip is

very challenging and will require careful

optimization or elimination of any always-on

components. Once the digital sub-system is

thoroughly power-gated, most of the leakage is

from analog/mixed-signal components. From the

start of the project, a tight budget has been set

Analog/mixed-signal block shutdown targets

Power control state machine - 2nW

Shutdown SRAM retaining 4KB - 2nW

Real-time clock, disabled or sub-kHz – 1nW

Integrated voltage regulator, including VREG

Two circuits chips were designed for silicon validation of these crucial building blocks, with

**Key Results**

clamps for equivalent protection of 2kV HBM

AMS blocks such as references functioning

correctly, will be included in battery monitor

rom chip 1 (taped out November 2017)

Achieved 50% lower leakage in new ESD

ROMs operating correctly below 300mV

To be improved further on chip 2 (May 2018)

• 10x IO pads on VBAT - 1nW

Battery monitor – 1nW Digital block shutdown targets

key results shown below.

and 400V CDM

ROM read speed

and voltage regulator

Shutdown SRAM leakage

for each block.

leakage – 3nW

THE ELECTRONICS **RESURGENCE INITIATIVE**

Distribution Statement A - Approved for Public Release, Distribution Unlimited