# Physical anti-tamper protection and passive sensor technologies

Geremy Freifeld (Draper PI), Murali Chaparala (Draper PI)

# Driving Applications: Supply Chain Hardware Integrity for Electronics Defense (SHIELD)

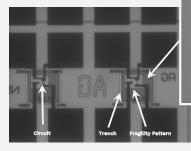

Custom BEOL Structure

**BEOL Cross Section**

### SHIELD enhanced fragility

Draper is developing critical hardware assurance features to combat the threat of counterfeit integrated circuit components entering the global electronics supply bracket is developing of the intervent association of values of cosmic at the intervent of cosmic thread intervent intervent of cosmic at the intervent of c

Example of Fragility process applied to a CMOS test wafer. CMOS Test wafer 10um ck, fragility pattern 7um dee

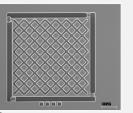

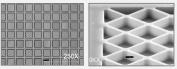

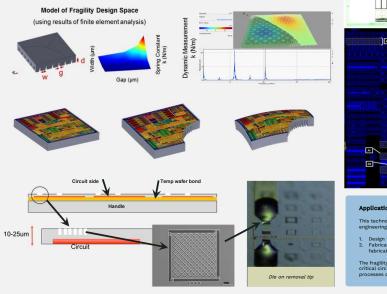

Different versions of fragility designs. Many iterations were manufactured and tested to c relate to the finite element analysis models. Some designs actually increased die strength!

#### Draper Fragility Enhancement Technology

The Draper fragility enhancement technology etches the backside of active CMOS regions of the SHIELD dielets. Fragility enhancement features are engineered to react to physical tampering and ensure either dielet physical fracture, or finite element analysis the fragility pattern is designed to reduce the normal uncontrolled variations in chip strength and insteadement tanubists the fragility pattern is designed to reduce the normal uncontrolled variations in chip strength and insteadement strength and the strength of the strength of the strength and instead allows highly engineered control/programmability of electromechanical properties that simultaneously achieves electrical robustness and physical fragility. Fragility enhancement designs must retain sufficient mechanical strength to survive the conditions of insertion into the host package, assembly, and normal use. Thus, the design is taliced to fail when it should fail, and survive when it should survive. The patterns etched into the SHELD dielets result in a 3 micron thickness in some portions of the active CMOS substrated

# Application of Fragility Enhancement Technology

This technology can be used to protect against reverse engineering of embedded IP.

Design fragility structures under the critical circuitry.

Fabricate the fragility structures after the circuit is fabricated at standard CMOS foundry.

The fragility structures can be designed to shatter the critical circuitry up on being subjected to physical FA processes or to alter the circuit performance.

## SHIELD Sensor | Objective and Concept

Main Objective: Passively detect and record environmental shifts in temperature & radiation for use in an advanced supply chain hardware authentication technology.

The sensor is based on a I/O 2T lateral single-poly floating-gate cell, schematically shown in Figure 1 with a crosssectional diagram shown in Figure 2. Quantum tunneling is used to initially program charge onto the floating-gate. As the sensor is exposed to energy, such as temperature elevation and radiation exposure, it will undergo mobile charge compensation, which will deplete the amount of charge stored proportional to the exposure

Charge loss sensitivity is tailored using custom back-end-of-line (BEOL) structures in device layout. A predictable correlation between charge loss and energy exposure is determined by the proportionality of the floating-gate surface area exposed to the interlayer isolation dielectric in the ASIC process

The device hits an asymptotic limit to charge loss below a specific energy threshold, which prevents the sensor from discharging in typical ambient environments.

\_\_\_\_\_

# Sensor Concept of Operation

- Sensor system is manufactured.

Initial program & calibration is performed at a trusted site and access to reprogramming is removed.

Device is packaged and pre-screened.

Device is sent to distributors for eventual assembly

- and depl

- User Site Sensor deployment Die level program & Passive thermal recording and read-ou Step 4 Step 1

CO SO

\_\_\_\_\_N

FG

Layout (Top-Down)

cg o-fl

\_\_\_\_\_

Dose in KRad(Si)

**RESURGENCE INITIATIVE**

THE ELECTRONICS

\_\_\_\_\_

# of Thermal Events

### **Radiation Test Approach & Results**

- X-ray source parameters

- Energy = 50KV

Filament current = 80uA

Distance = 3cm

No collimator

- Time/distance exposure corresponds to a dose of

- ~1KRad(Si)

A 700Rad(Si) exposure would cause a similar voltage shift as a high-temp thermal event. Depending on the material, the package & lid will provide varying levels of shielding. I.e. 10mils of Kovar would provide 100% shielding for this testing.

Typical imaging exposure levels using micro computed tomography ( $\mu CT$ ) are in the 20Krad range. Appreciable operational degradation would also require exposure levels in excess of 10KRad. Any require exposite teres the second of the sec

Application of Floating Gate Sensor Technology This technology can be used to detect warranty nulling exposure of electronics to high temperature or to radiation. The floating gate technology can be adapted to detect exposure to various chemistries, light, et

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.