**Development Framework for Next Generation High-Performance Processors** Domain-Focused Advanced Software-Reconfigurable Heterogeneous SoC (DASH - SoC)

Daniel Bliss & et al.

Arizona State Univ., Arm, Carnegie Mellon Univ., EpiSys Sciences, General Dynamics, Univ. of Arizona, & Univ. of Michigan

## Architectures Thrust: Domain-Specific System on Chip (DSSoC)

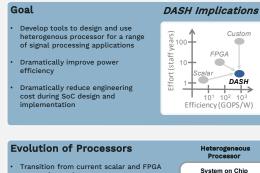

## **DASH Project Statement**

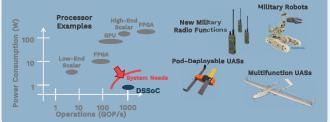

The DASH-SoC team drives a revolution in flexible DSSoC computational systems. To support unmanned aerial, small robotic or leave-behind, and universal soldier systems, the Department of Defense (DoD) needs reduced size, weight, and power (SWaP). To support multifunction systems (communications, sensing, positioning, SIGINT, EW), the DoD requires dramatically increased processing flexibility. We break the fundamental trade that custom SoCs are required for power efficiency. but scalar processors are required for ease of implementation.

## Impact

- Enable wide range of new applications that require many TOP/s such as:

- Advanced SIGINT, modern communications → ~ 1000 GOP/s

- Bistatic SAR, match filter → ~ 1000 GOP/s

- Advanced video processing, 8k video image alignment  $\rightarrow$  ~ 1000 GOP/s Support new and evolving types of DoD users (human and non-human)

- Quickly address new problems as they arise

Prof. John Brunhaver Prof. Chaitali Chakrabarti<sup>1</sup> Prof. Ronald Dreslinski<sup>7</sup> Mr. John Fielden<sup>5</sup> Dr. Matt Horsnell<sup>2</sup> rof. David Blaauw Ir. Lee Eisen<sup>2</sup> Mr. Tom Genduso Prof. Hun-Seok Kim Dr. John Goodenough Mr. Allen E. Lacey<sup>6</sup>

Prof. Radu Marculescu<sup>3</sup> Arizona State University Prof. Trevor Mudge<sup>1</sup> <sup>2</sup>Arm, Ltd. Prof. Umit Y. Ogras <sup>3</sup>Carnegie Mellon University Dr. Nadeesha Ranasinghe <sup>4</sup>EpiSys Sciences, Inc. <sup>5</sup>General Dynamics Mission Systems r. Bo Ryu Mr. Donald L. Westhafer<sup>5</sup> 6University of Arizona University of Michigan

Innovation Overview

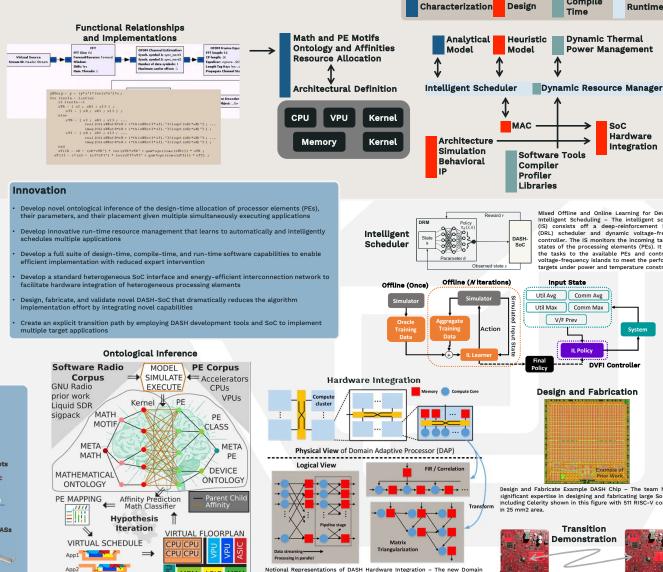

Intelligently Translate Corpus of System Specifications to Identify Processing Elements and Connections - Device and mathematical knowledge are statistically derived from a body of applications and hardware designs, resulting in taxonomies and an understanding of math's affinity for a PE. A hypothetical SoC design and schedule proposed using a classification of the program's components and a prediction of their performance on a specific device.

Adaptive Processor (DAP) are heterogeneous PEs are integrated within the

DASH SoC. DAP is run-time transformable from the physical view (top) to various logical configurations (bottom) supporting dynamic compute /

memory resource allocation and various streaming data movement patterns.

Hierarchical crossbars in a DAP are fast reconfigurable to realize various

Mixed Offline and Online Learning for Developing Intelligent Scheduling – The intelligent scheduler (IS) consists off a deep-reinforcement learning (DRL) scheduler and dynamic voltage-frequency controller. The IS monitors the incoming tasks and states of the processing elements (PEs). It assigns the tasks to the available PEs and controls the voltage-frequency islands to meet the performance targets under power and temperature constraints.

SoC

Hardware

Integration

Input State Util Avg Comm Avg Util Max Comm Max V/F Prev IL Policy ----<sup>1</sup> DVFI Controller

Compile

Runtime

**Design and Fabrication**

Design and Fabricate Example DASH Chip - The team has significant expertise in designing and fabricating large SoCs. Including Celerity shown in this figure with 511 RISC-V cores

Over-the-Air DASH-SoC Software-Defined Radio Experiments - A development board using the DASH-SoC is developed and used to demonstrate implementation and performance advances. This also provides an initial path to transitio

domain-specific systolic data pipelines.