## Impact: If Successful ...

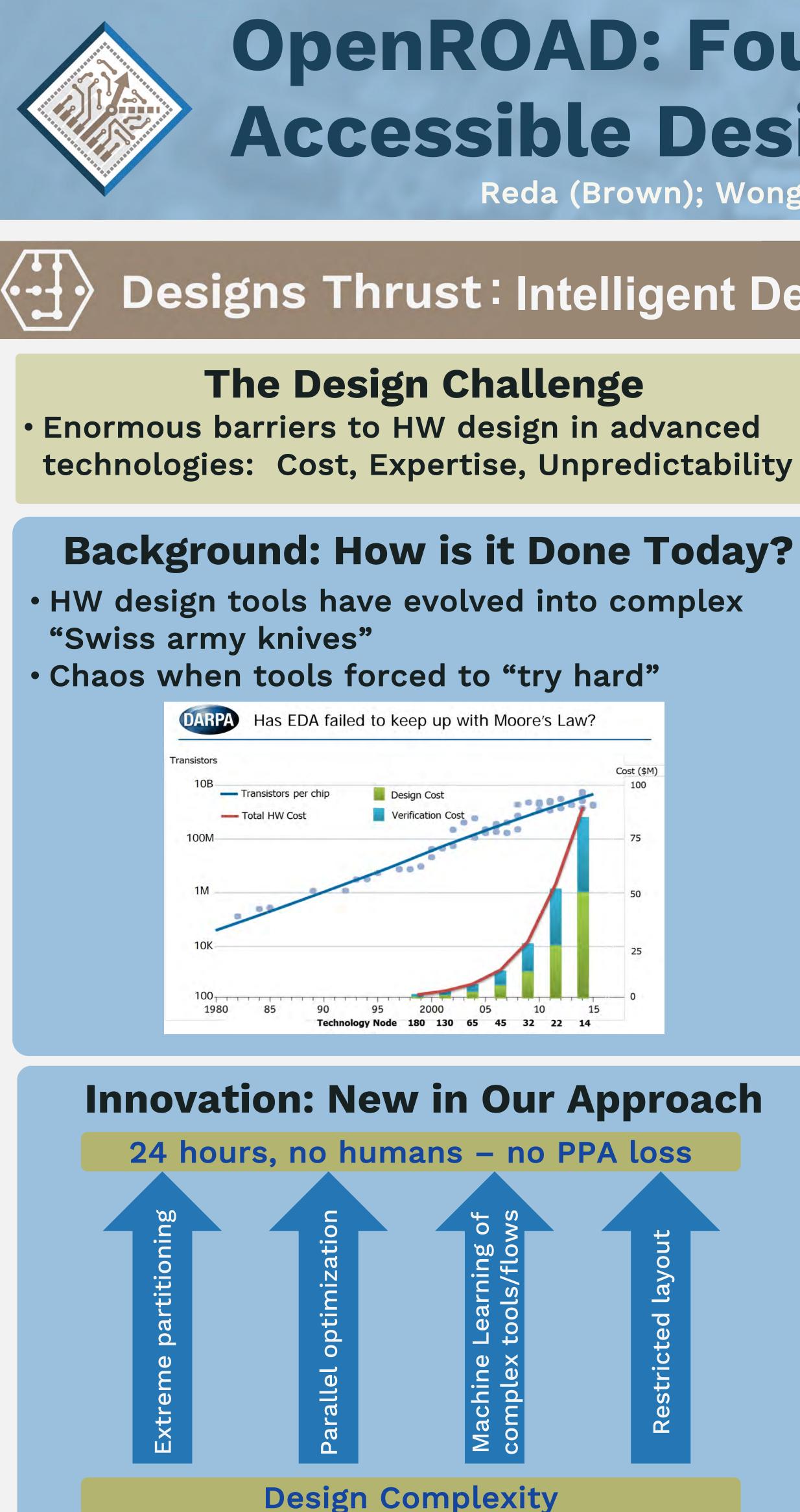

- Create new "Base Technologies" that enable 24-hour, autonomous design

- Extreme partitioning (bite-sized problems)

- Parallel search, optimization

- Machine learning: models of tools, designs • Change paradigm for tools + design methods:

- autonomy first • Bring down barriers  $\rightarrow$  democratize HW design

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

**OpenROAD: Foundations and Realization of Open,**

Accessible Design Kahng [PI], Saul (UCSD); Penzes, Vaishnav, Chan (Qualcomm), Coltella, Urquhart, Aitken (Arm) Reda (Brown); Wong (Illinois); Sylvester, Blaauw, Dreslinski (Michigan); Sapatnekar (Minnesota); Sechen, Swartz (UT-Dallas)

# **Designs Thrust: Intelligent Design of Electronic Assets (IDEA)**

## **Our Goal**

- •24-hour, No-Human-In-Loop layout for SOC, Package and PCB with no Power-Performance-Area (PPA) loss

- Tapeout-capable tools in source code with permissive licensing future "Linux of EDA"

### **Foundations of Approach**

- No humans: tools must adapt and self-tu must never get stuck unexpectedly

- 24 hours: extreme partitioning of problem parallel search on cloud + machine learni predictability

- Mantra: Correctness and safety by constr

- Mantra: Embrace freedom from choice

#### **Technical Challenges**

- Data: small and expensive!

- Humans: in the loop for good reasons!

- Fundamental tradeoffs: analysis cost vs. accuracy, optimization effort vs. quality

- Activation energies: new sharing mindset open-source ecosystem

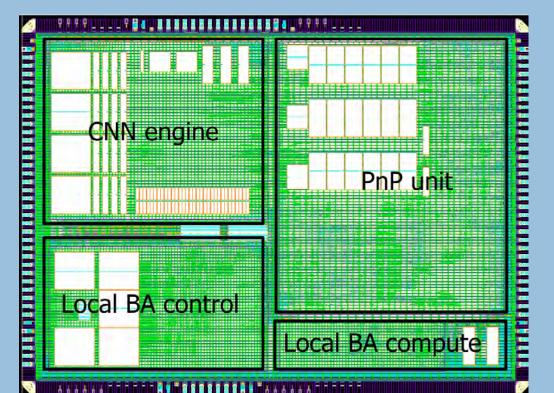

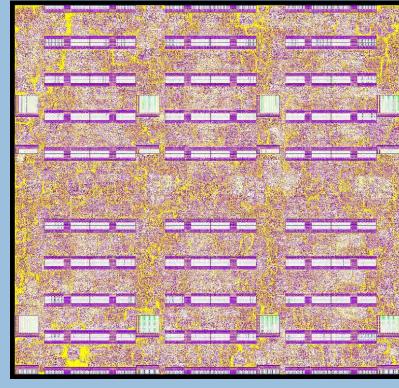

#### Impact on Design Cost

- Embedded vision chips (28/16nm) from M Internal Design Advisors team

- Layout @UM: 10+ weeks, significant resource

- OpenROAD and IDEA goal: 1 day, no humans (!)

| design                     | • Need critical                                                                                                                                                                                                                                                                                                                                                                                | <b>In ass <u>and</u> critical qu</b><br>1 of 13 IDEA TA-1 sub      |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| le form,<br>→ seed         | ✓                                                                                                                                                                                                                                                                                                                                                                                              | Databases / Processing<br>Cloud Infrastructure<br>Timing Analysis  |

| une,                       | ✓                                                                                                                                                                                                                                                                                                                                                                                              | Parasitic Extraction<br>Readers + Writers<br>Power and SI Analysis |

| ms +<br>ing for<br>ruction | Generators                                                                                                                                                                                                                                                                                                                                                                                     | Logic Synthesis<br>Floorplanning<br>Placement                      |

|                            | ✓                                                                                                                                                                                                                                                                                                                                                                                              | Clock Tree Synthesis<br>Detailed Routing<br>Layout Finishing       |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                | SoC Design Advisors                                                |

| ts,                        | <ul> <li>~70 Ph.D. / 50 M.S. graduates</li> <li>+ 15+ new SOC designs/year</li> <li>• Tools team from UCSD, Illinois,<br/>Minnesota, UT-Dallas, Brown:</li> <li>Ph.D. / 80 M.S. graduates</li> <li>many tools, engines "on the shelf</li> <li>• Qualcomm: HW design expertise</li> <li>• Arm: system, IP expertise</li> <li>• And more:</li> <li>• Open-sourced commercial timing e</li> </ul> |                                                                    |

|                            |                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |

| Aichigan                   | <ul> <li>Open-sourced commercial timing e</li> <li>Donated commercial source code b</li> <li>Industry advisors, technical contrib</li> <li>Worldwide outreach and engageme</li> </ul>                                                                                                                                                                                                          |                                                                    |

| urce                       |                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |

Distribution Statement A – Approved for Public Release. Distribution Unlimited