# **Fully-Autonomous SoC Synthesis using Customizable** Cell-Based Synthesizable Analog Circuits PI: Prof. David Wentzloff (UM); Co-PI: Prof. David Blaauw (UM), Prof. Dennis Sylvester (UM), Prof. Ron Dreslinski (UM), Prof. Ben Calhoun (UVA), Matteo Coltella (ARM), David Urguhart (ARM),

## Designs Thrust: Intelligent Design of Electronic Assets (IDEA)

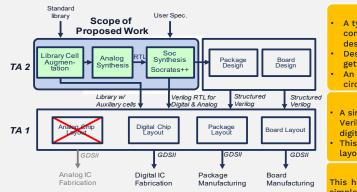

The proposed research will develop a fully-autonomous SoC synthesis tool using customizable cell-based synthesizable analog circuits for IDEA Technical Area II. Our approach leverages a differentiating technology to synthesize "correct-byconstruction" Verilog descriptions for both analog and digital circuits to enable a portable, single pass implementation flow.

A typical SoC has many analog components, which have labor intense design processes Design in advanced nodes (<28nm) is getting harder An SoC synthesis tool realizes analog circuit automation is desired

Background

#### Innovation

A single SoC synthesis tool that produces Verilog descriptions for both analog and digital components This RTL is passed only to the digital chip

layout tool for APR

Impact

This has the advantage of creating a much simpler, unified back-end design flow and improving design portability to advanced technology nodes

Figure 1. Scope of the proposed work, showing its fit into the BAA technical areas.

#### **PREVIOUS WORK & DESIGN GOAL**

Our group has been working on synthesizable circuits, such as: ADPLL, TDC, IR UWB Transmitters, DAC, and Serial Links. The following are selected previous synthesized works, and our goal of research

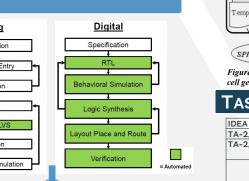

|                    |                            | Analog                                                  | Digital                |

|--------------------|----------------------------|---------------------------------------------------------|------------------------|

| 170 µm             |                            | Specification                                           | Specification          |

| 190 µm             |                            | Schematic Entry                                         |                        |

|                    |                            | Simulation                                              | Behavioral Simulation  |

|                    | imm >                      |                                                         | Logic Synthesis        |

| Synthesized UWB TX | Synthesized Serial Link    | DRC and LVS                                             | Layout Place and Route |

|                    | LVDS                       | Extraction                                              | ↓<br>Verification      |

| A mm               | Receiver DAC Core<br>Clock | Post-layout Simulation                                  |                        |

|                    | Gen,                       | Propose a fully-autonomo                                | us SoC synthesis too   |

| Synthesized ADPLL  | Synthesized DAC            | replace the time consumin<br>developed from the previou |                        |

| Synthesized ADFLL  | Synthesized DAC            | advanced Finfe                                          |                        |

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

l to

#### **PROPOSED RESEARCH**

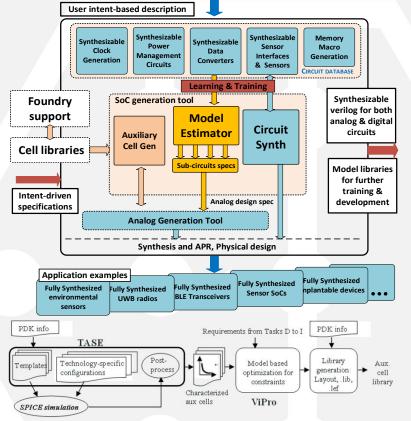

Figure 2. Block diagram of proposed research showing the interactions among tasks and the proposed auxiliary cell generation flow

### **TASK AND MILESTONES**

| IDEA TA-2 Sub-task                           | Proposal Tasks                                  |  |  |

|----------------------------------------------|-------------------------------------------------|--|--|

| TA-2, Sub-task 1: Open parts database        | Extending IP-XACT, Synthesizable Circuit Blocks |  |  |

| TA-2, Sub-task 2: System generator           | Extending Socrates Infrastructure, Correct-by-  |  |  |

|                                              | Construction Design                             |  |  |

|                                              | Synthesizable Clock Generation                  |  |  |

|                                              | Synthesizable Power Management                  |  |  |

|                                              | Synthesizable Data Conversion                   |  |  |

| TA-2, Sub-task 2: Reference design generator | Synthesizable Sensor Interfaces                 |  |  |

|                                              | Synthesizable Thermal Sensors                   |  |  |

|                                              | Memory Macro Generation                         |  |  |

|                                              | Auxiliary Cell Generation                       |  |  |

| TA-2, Sub-task 3: Circuit optimizer          | Circuit Block optimization                      |  |  |

|                                              |                                                 |  |  |

**UNIVERSITY** *d* **VIRGINIA**

UNIVERSITY OF MICHIGAN Distribution Statement A - Approved for Public Release, Distribution Unlimited