CLEARED

For Open Publication

Aug 17, 2020

Department of Defense

FFICE OF PREPUBLICATION AND SECURITY REVIEW

## Trusted and Assured Microelectronics Program

Create a Robust and Resilient Pipeline

Matthew Casto, Ph.D.

Program Director, Trusted and Assured Microelectronics

NO SCRIET PROVIDED

**DARPA ERI Summit**

August 2020

https://www.CTO.mil

@DoDCTO

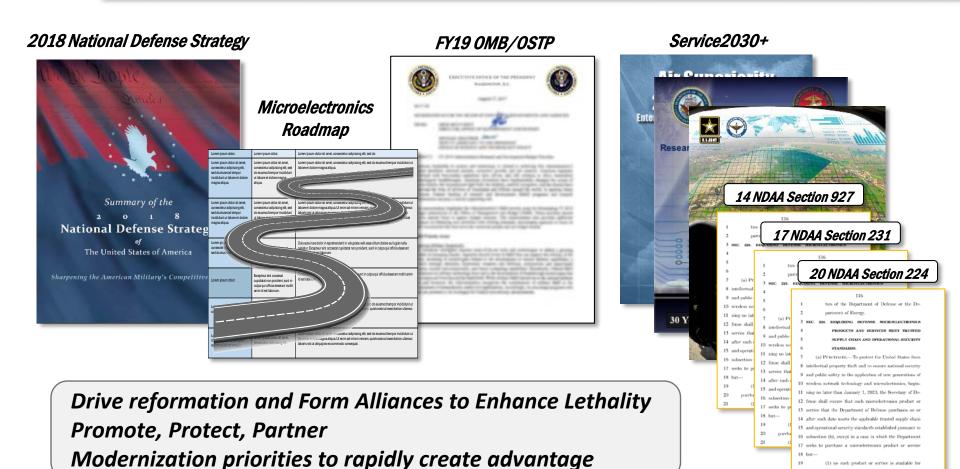

#### **Strategic Guidance**

Microelectronics is DoD's Top Modernization Priority!

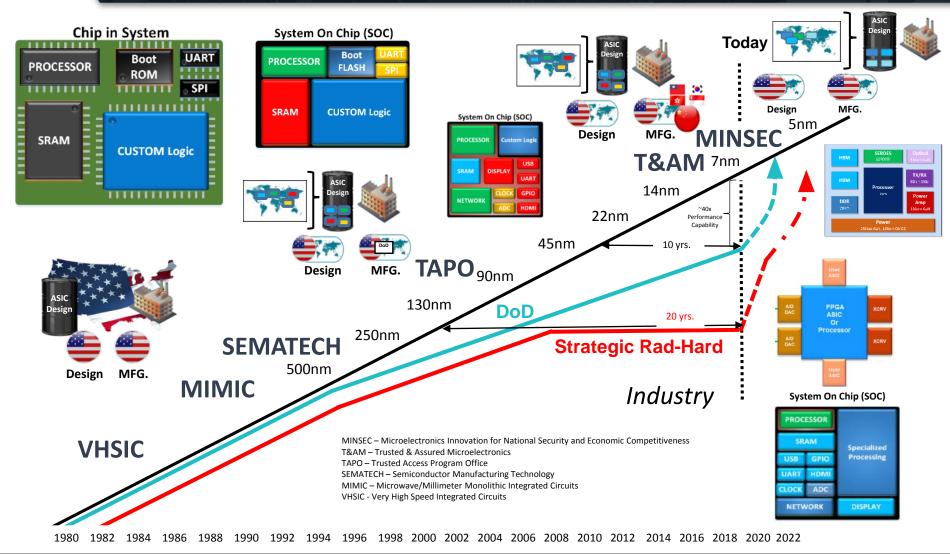

#### **Assured Microelectronics Evolution**

T&AM/MINSEC Program is developing the secure ecosystem to assure SOTA performance for Modernization

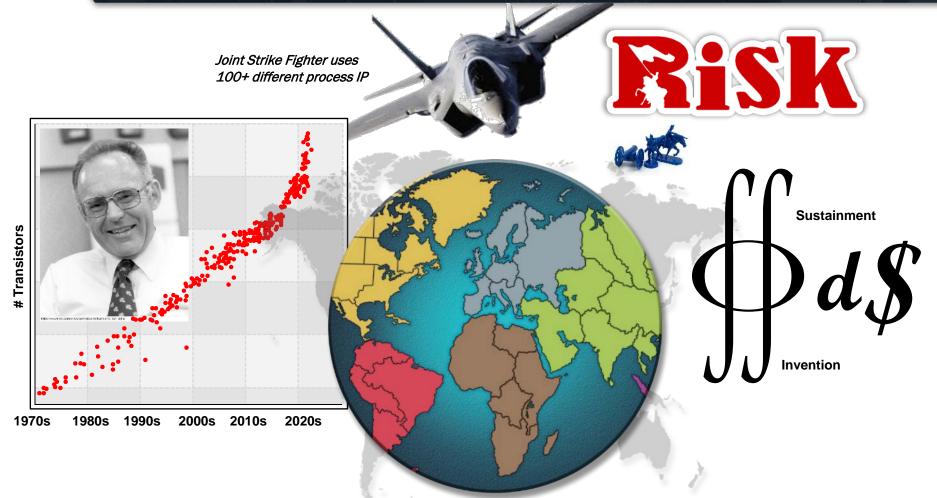

#### Microelectronics Landscape

Specialization of Electronics - Risk in Global Supply - Changing the Lifecycle Speed & Cost Efficiency

## Trusted and Assured Microelectronics Strategic Approach

#### **Microelectronics - DoD's Top Modernization Priority**

We cannot expect success fighting tomorrow's conflicts with yesterday's weapons or equipment.

-National Defense Strategy

Access to State of the Art Commercial Technology

Data Driven

Quantifiable Assurance

Address DoD Unique Needs

Create a Resilient and Robust Pipeline

Gaps: DoD lags commercial CMOS ecosystem/ infrastructure

Threats to design and manufacturing in global supply chain

Increased sources for national strategic defense

Domestic and Allied Ecosystem to rapidly and securely mature emerging advanced technology

Approach:

Establish best practices for secure design, assembly, packaging, and test capabilities to support DIB and co-development of dual use electronics

Secure full lifecycle confidentiality, Integrity, verification & validation, and supply chain for assured warfighters electronics

Develop sustainable sources of mission essential niche radhard electronics capabilities, and specialized radio frequency and electro-optic components Invigorate secure pipeline for disruptive R&D transition, supply chain aware technology development, education and workforce.

#### **Current T&AM Challenges**

- Lower barriers to specialization and innovation in advanced IC technologies; Tools, Intellectual Property, Fabrication

- Attract, recruit and retain talented STEM workforce with knowledge of DoD-specific challenges

- Identify & mitigate supply chain threats to improve assurance & resilience of microelectronics

- Rapidly mature, co-develop, and transition new and emerging technologies with assurance and security for program adoption

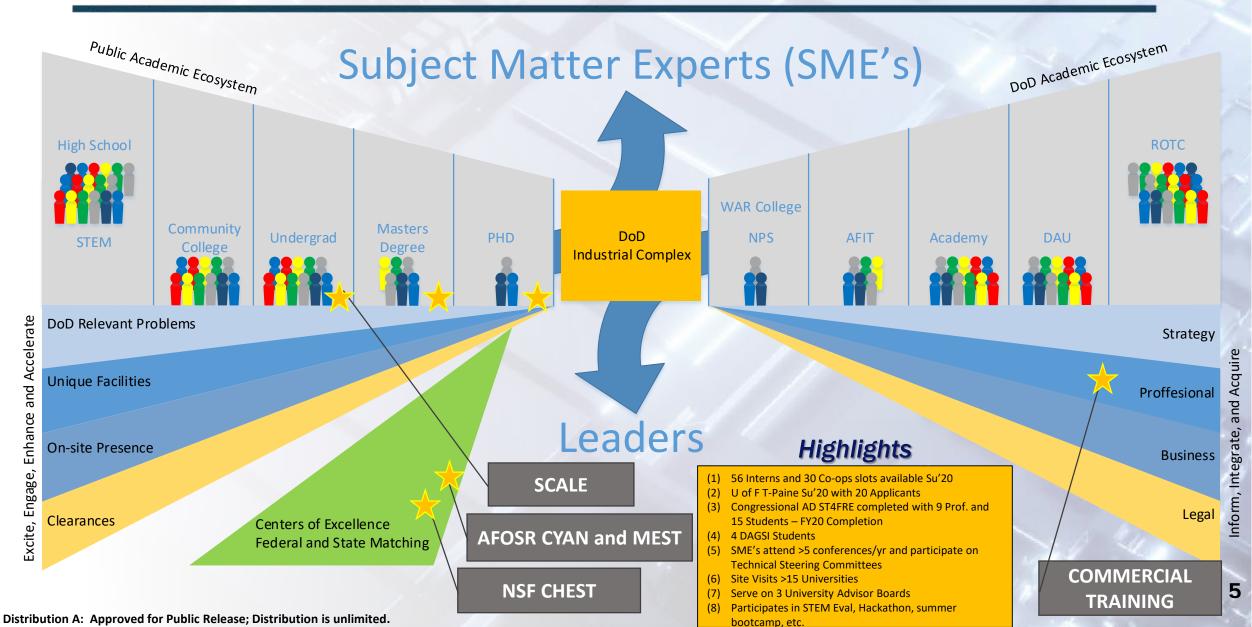

#### **Create a Resilient and Robust Pipeline**

Invigorate secure pipeline for disruptive R&D transition, supply chain aware technology development, education and workforce.

DARPA

#### **Innovation Accelerators**

- Engage with non-traditional technology sources to cultivate a SOTA microelectronics ecosystem, built on a foundation of assurance

- •Technology for DoD Asymmetric Advantage

- DoD Asymmetric Advantage; Sustainable US company

#### Education and Workforce Development

- Outreach to universities to develop US-based semiconductor-focused education pipelines; Semiconductor Fab, Security/Assurance, Design, Package, and Test

- •Education and Training for DoD and DIB

#### Supply Chain Awareness and Security

- Addressing security to risk supply chain through tech development, V&V, and CI awareness; Briefings to DIB partners and industry

- Improve Supply Chain Awareness

- •Intelligence prep of the Battlespace

- Counterintelligence Execution

#### Technology Development

- Leverage SOTA commercial technology to co-develop assured solutions

- •Adapt SOTA technology to enable DoD Unique solutions

- Accelerate on shore availability and development for adoption in DoD PoR

- Compute Platforms, Domain Specific Tech, Supply Chain Solutions, Programmable Logic

Program\*

Development &

Capabilities

PPP\*/

Design

Verify

Mask

**Fabrication**

Pack. & test

Verify & validate

Config. prog. SW

Integrate & test

Operation & maint.

UNCLASSIFIED

## T&AM: Create a Robust and Resilient Microelectronics Pipeline Panel Agenda

- 1415 1435 Introduction

- Dr. Matthew Casto, T&AM Program Director

- 1425 1600 Education and Workforce Development Consortium Panel

- Allison Smith, Naval Surface

Weapons Center Crane, T&AM

Technical Execution Lead

- Panel Members NSS IECRC,

Universities Cincinnati, Purdue,

Florida and Ohio

- 1600 1615 AFTERNOON BREAK

- 1615 1645 OSD and AF Microelectronics Design and Prototype Challenge

- Vipul J. Patel, AFRL, Sr. ElectronicsEngineer

- 1645 1715 Technology Development

- Peter O'Donnell, Army Combat Capabilities Combat Command, T&AM Technical Execution Area

- 1715 1745 Supply Chain Awareness and Security

- Adam Hauch, Naval Surface

Weapons Center Crane, Technical

Execution Area Lead

- 1745 1845 Virtual Demo & Poster Session

## T&AM: Create a Robust and Resilient Microelectronics Pipeline Panel Agenda

- 1415 1435 Introduction

- Dr. Matthew Casto, T&AM Program Director

- 1425 1600 Education and Workforce Development Consortium Panel

- Allison Smith, Naval Surface

Weapons Center Crane, T&AM

Technical Execution Lead

- Panel Members NSS IECRC,

Universities Cincinnati, Purdue,

Florida and Ohio

- 1600 1615 AFTERNOON BREAK

- 1615 1645 OSD and AF Microelectronics Design and Prototype Challenge

- Vipul J. Patel, AFRL, Sr. ElectronicsEngineer

- 1645 1715 Technology Development

- Peter O'Donnell, Army Combat Capabilities Combat Command, T&AM Technical Execution Area

- 1715 1745 Supply Chain Awareness and Security

- Adam Hauch, Naval Surface

Weapons Center Crane, Technical

Execution Area Lead

- 1745 1845 Virtual Demo & Poster Session

# Education & Workforce Development Panel

Session: Trusted and Assured Microelectronics (T&AM): Create a Resilient and Robust Microelectronics Pipeline

#### Panel Discussions - Housekeeping

- If you have non-technical issues, please contact the <u>CO-HOSTS</u> identified as <u>FACILITATORS</u>

- All conversations must remain at Distribution A level (no classified, FOUO, CUI, etc.)

- Microphones will be muted and videos disabled for attendees.

- For questions or comments to the panel members, please use the <u>Q&A Feature</u>

- If you have a question for the speaker or would like to share insights, please use the "Q&A Feature".

- The presenter will answer your question or comment on your insights.

- You will have 60 seconds to ask your question or share you insights.

- If you dial-in separately using your phone, please link the phone connection with your assigned participant ID

- The participant ID is the 6 numbers seen by clicking on the in the upper left of the Zoom screen

- On your phone, press #, enter the participant ID, and press #

- If you have any logistical or connection issues:

- Connect with Zoom support:

- Zoom Troubleshooting Guidance: https://support.zoom.us/hc/en-us/sections/200305593-Troubleshooting

- Wireless Connection Issues: https://support.zoom.us/hc/en-us/articles/201362463-Wireless-WiFi-Connection-Issues

- Connect with the ERI Team desk via the 6Connex platform

# Dr. Alison Smith NAVAL SURFACE WARFARE CENTER, CRANE DIVISION (NSWC CRANE)

Mr. Len Orlando

AIR FORCE RESEARCH LABORATORY

(AFRL)

T&AM EDUCATION & WORKFORCE DEVELOPMENT EXECUTION CO-LEADS

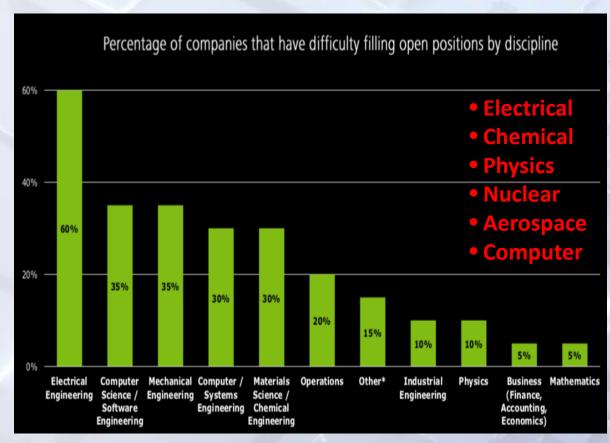

#### The War for Talent

#### T&AM STEM Discipline Needs

- Lowest overall student representation

- Largest influx of international students

"As much as emerging technologies will define future conflict, *the war for talent will likely play the central role* in the outcome of long-term technological competition.

The National Security Innovation Base (NSIB) struggles to attract, recruit, and retain a workforce willing and able to tackle tough challenges and find innovative solutions. Universities are confronting a dearth in American talent generation and retention."

Source: Engineering Talent Shortage Now Top Risk Factor, Semiconductor Engineering, Deloitte Survey, Feb. 25, 2019

T&AM Has Unique Interdisciplinary Needs Within A Competitive STEM Market

#### **T&AM Education & Workforce Development**

#### **Education & Workforce Development Panel**

- Prof. Marty Emmert, NSF IUCRC CHEST (Center for Hardware and Embedded System Security and Trust)

- Prof. Mark Tehranipoor and Prof. Waleed Khalil, AFOSR MEST/CYAN (The National Microelectronics Security Training Center and the Center for Enabling Cyber Defense in Analog and Mixed Signal Domain)

- Dr. Praveen Chawla, Edaptive Computing Inc.

- Ms. Cheyanne Harshman, Centauri Corp.

- Prof. Peter Bermel, SCALE (Scalable Asymmetric Lifecycle Engagement)

- Prof. Carolyn Goerner, Best Practices in Talent Management

#### Panel Discussions - Housekeeping

- If you have non-technical issues, please contact the <u>CO-HOSTS</u> identified as <u>FACILITATORS</u>

- All conversations must remain at Distribution A level (no classified, FOUO, CUI, etc.)

- Microphones will be muted and videos disabled for attendees.

- For questions or comments to the panel members, please use the <u>Q&A Feature</u>

- If you have a question for the speaker or would like to share insights, please use the "Q&A Feature".

- The presenter will answer your question or comment on your insights.

- You will have 60 seconds to ask your question or share you insights.

- If you dial-in separately using your phone, please link the phone connection with your assigned participant ID

- The participant ID is the 6 numbers seen by clicking on the in the upper left of the Zoom screen

- On your phone, press #, enter the participant ID, and press #

- If you have any logistical or connection issues:

- Connect with Zoom support:

- Zoom Troubleshooting Guidance: https://support.zoom.us/hc/en-us/sections/200305593-Troubleshooting

- Wireless Connection Issues: https://support.zoom.us/hc/en-us/articles/201362463-Wireless-WiFi-Connection-Issues

- Connect with the ERI Team desk via the 6Connex platform

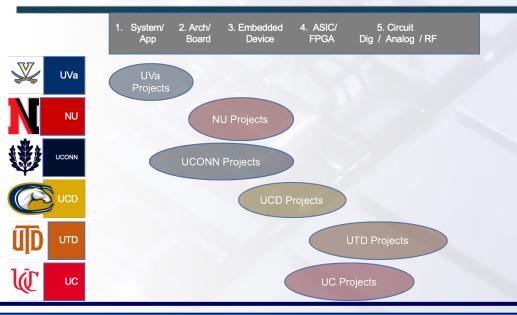

# NSF Center for Hardware and Embedded Systems Security and Trust (CHEST) IUCRC

## John (Marty) EMMERT

PROFESSOR, UNIVERSITY OF CINCINNATI DIRECTOR, CHEST IUCRC

#### **NSF CHEST IUCRC**

#### Description of Project and link to T&AM Mission

- Coordinates university-based research with needs of industry and government partners to advance knowledge of microelectronic security, assurance, and trust (SAT)

- Identification, detection, monitoring, mitigation, and elimination of vulnerabilities that affect electronic hardware and embedded systems

#### How is this better than current SOTA

- With industry oversite, the CHEST Center addresses a range of attack vectors across design, operation, manufacturing, supply chains, and integration of the HW, SW, and firmware

- Limited 10% overhead: 90% of all funds go directly to research

- Minimal time required to get projects "on contract"

- Educating the next generation of experts

- Collaborative environment: DoD / Industry / NSF / Academia

#### Funding Overview & Key Partnerships

POC: Dr. J. M. Emmert (Marty), University of Cincinnati

email: John.Emmert@uc.edu

Mr. Luis Concha, University of Cincinnati

Email: Luis.Concha@uc.edu

|     | 2020  | 2021  | 2022  | 2023  | 2024  |

|-----|-------|-------|-------|-------|-------|

| Fee | \$50k | \$50k | \$50k | \$50k | \$50k |

Requirements: Membership Support, IAB Oversite, Data

IAB Leads: Len Orlando and Brian Dupaix, AFRL

CHEST Team: Marty Emmert, Director (UC), Houman Homayoun (UC Davis), Yunsi Fei

(NU), John Chandy (UCONN), Yiorgos Makris (UTD), James Lambert (UVa)

#### Approach

- <u>Technical</u>: The NSF CHEST Center addresses security, assurance, and trust across several levels: Large-scale systems, embedded systems, design and operations, requirements, standards, manufacturing, supply chains, and integrated circuits and boards.

- <u>Contract</u>: Vehicle: MIPR (DoD) or Check (Industry)

https://www.nsf.gov/eng/iip/iucrc/government.jsp

https://www.nsf.gov/eng/iip/iucrc/iaainstructions.jsp

#### Benefits / Deliverables

- Monthly / Quarterly / Annual Reports and Updates

- Royalty free access to IP: Standard NSF IUCRC MOU

- HW / SW / Testbed Demonstrations

- WF Development: Next generation of SMEs in the area of Security, Assurance and Trust for Electronic HW and Embedded Systems

#### 2020 CHEST Inaugural Projects

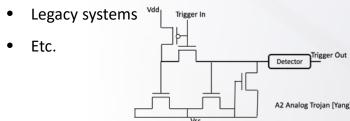

#### What types of problems does CHEST address?

- Any basic or applied research related to SAT

- SCA: detection, prevention, mitigation

- Trojan: detection, prevention, mitigation (eg. =>)

- Reverse engineering: ASIC (physical destructive/nondestructive) and FPGA bitstreams

- Integrated circuit and silicon authentication

- Anti Tamper: detection, prevention, mitigation

- Countermeasure design / methodologies

- PUFs (physical unclonable functions)

- Intellectual Property: protection, anti-cloning, anti-counterfeiting, over-manufacturing, piracy etc.

- Assessment: metrics for levels of TRUST

- Embedded algorithm protection

Distribution A: Approved for Public Release; Distribution is unlimited.

- P1\_20: Asynchronous Design for Side Channel Avoidance (\$100K); J. M. Emmert (john.emmert@uc.edu), Ranga Vemuri (UC)

- P2\_20: Connectionless RFID based Secure Supply Chain Management (\$50K); Marten van Dijk (marten.van\_dijk@uconn.edu), Ulrich Ruhrmair (UConn)

- P3\_20: Reverse Engineering Methodology for FPGA Bitstreams (\$100K); James H. Lambert (UVa), Zachary Collier, J. M. Emmert (john.emmert@uc.edu), Carla Purdy (UC)

- P4\_20: Additive Components for Hardware Integrity

Monitoring (\$100K); Rashmi Jha (<a href="mailto:jhari@ucmail.uc.edu">jhari@ucmail.uc.edu</a>), Marc

Cahay, Punit Boochand (UC)

- P5\_20: Cost-Effective Resource Allocation to Portfolios of Security Measures for Embedded Devices in a Large-Scale System (\$25K); James H. Lambert (jhl6d@virginia.edu), Dr. Zachary A. Collier, Mr. Thomas A. Polmateer (UVA)

- P6\_20: Trusted Enterprise Communications and Cyber-Physical Integration of Advanced Fleet Electrical Vehicle Chargers in a Mobile Electric Grid (\$95K); James H. Lambert (<a href="mailto:jhl6d@virginia.edu">jhl6d@virginia.edu</a>), Dr. Zachary A. Collier, Mr. Thomas A. Polmateer (UVa)

- P7\_20: CAD Flow Development for Design Obfuscation through Post-Fabrication Transistor-Level Programming (TRAP) (\$100K); Yiorgos Makris (yiorgos.makris@utdallas.edu), Carl Sechen, Benjamin Carrion Schaefer, William Swartz (UTD)

- **P8\_20**: Design Obfuscation and Performance Locking Solutions for Analog/RF ICs (\$75K); **Yiorgos Makris** (yiorgos.makris@utdallas.edu), Ken O, Andrew Marshall (UTD)

- P9\_20: Formal Security Evaluation of Executing Untrusted Binaries on Embedded Processors (\$50K); Kevin Hamlen, Yiorgos Makris (yiorgos.makris@utdallas.edu) (UTD)

- P10\_20: Stochasticity, Polymorphism and Non-Volatility: Three Pillars of Security and Trust Intrinsic to Emerging Technologies (\$50K); Joseph Friedman, Yiorgos Makris (yiorgos.makris@utdallas.edu) (UTD)

- P11\_20: Secure Design by RISC-V Framework (\$70K); Yunsi Fei (yfei@ece.neu.edu), David Kaeli (NU)

- P12\_20: Current Sensing Based On-chip Analog Trojan Detection Circuit Compatible with Chip Design and Validation Flow (\$50K); Aatmesh Shrivastva (aatmesh@ece.neu.edu), Yunsi Fei (NU)

- P13\_20: Cognitive Obfuscation: Securing Circuits by Graph Convolutional Networks (\$100K); Houman Homayoun (<a href="mailto:hhomayoun@ucdavis.edu">hhomayoun@ucdavis.edu</a>) (UC Davis), Venkatesh Akella (UC Davis)

- **P14\_20**: A Neural Network Assisted Timing Profiling for Hardware Trojans Detection (\$75K); **Houman Homayoun(hhomayoun@ucdavis.edu)** (UC Davis)

- P15\_20: Embedded Systems Anti-Reverse Engineering using Transient Electronics (\$50K); Lei Wang, John Chandy (john.chandy@uconn.edu) (UConn)

- P16\_20: Leveraging Hardware Isolation for Secure Execution of Safety-Critical Applications in Distributed Embedded Systems (\$50K); Omer Khan (khan@uconn.edu) (UConn)

## Waleed KHALIL

PROFESSOR – OHIO STATE UNIVERSITY

CO-DIRECTOR OF CYAN AND MEST

CENTERS OF EXCELLENCE

## Center of Excellence for Cyber Defense in the Analog and Mixed Signal (AMS) Domain (CYAN)

#### **Research Program & Team**

- Strong & diverse expertise in hardware security, AMS design, fabrication, test, electromagnetics, applied cryptography, machine learning and data analytics

- Holistic research approach in securing the design, fabrication, and operation of AMS technologies and analog emissions

#### **Education & Capacity Building**

- New generation of workforce exposed to multidisciplinary environment of modern-day scientific research

- Target 20 PhD/MS students + 20 undergraduates (50% US)

- 18 PhD/MS students currently affiliated with the center: 11 receive direct CYAN funding and 7 from external sources (10 US students in total)

#### **Government & Industry Partnership**

- Consortium-led cooperation with national labs, commercial and defense industry

- Grow research funding to sustain CYAN beyond 5 years

- Leverage add'l funding to amplify the research: 1 funded project/ 5 pending

#### **CYAN Thrust 1: Securing AMS Devices & Systems**

- AMS Security Primitives

- AMS Obfuscation

- AMS Counterfeit & Trojan Detection/Prevention

- Analog Enabled Cryptography

- Securing Power Supplies

### CYAN Thrust 2: Exploiting Analog Emanations for Cyber Defense

- RF and Process Authentication

- Electromagnetic

Signatures from AMS

Devices

- Program Analysis via Side-channel Signals

- Side Channel Assessment

## Mark TEHRANIPOOR

INTEL CHARLES E. YOUNG ENDOWED CHAIR PROFESSOR – UNIVERSITY OF FLORIDA

DIRECTOR FOR FICS RESEARCH, CO-DIRECTOR FOR CYAN AND MEST CENTERS OF EXCELLENCE

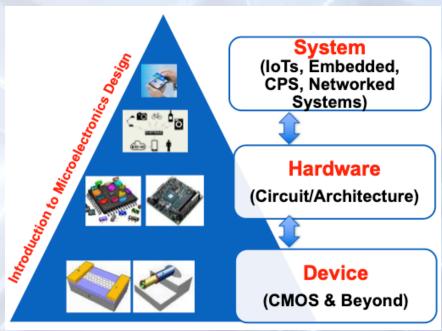

#### MEST: National MicroElectronics Security Training Center

#### **Research Program & Team**

- Increasing demand for well-trained cybersecurity workforce in all government agencies, national labs, and industry sectors!

- MEST offers a comprehensive training effort in microelectronics security is a critical need

- Outstanding team of faculty and industry practitioners offering webinars, long, and short courses

#### **Education & Capacity Building**

- New generation of workforce exposed to multidisciplinary environment of modern-day scientific research

- Total attendees (Webinar + Certificate Trainings): 2000+

- 16 webinars, 8 trainings, and 5 online courses developed so far

#### **Government & Industry Partnership**

- Develop and provide <u>free</u> training programs on microelectronics design and security to the Government and Defense Industrial Base

- We plan to establish a consortium of companies sponsoring MEST in the future

- Cybersecurity Case Studies

- Secure Architecture Design

- Automotive Security

- Cross Layered Systems Security

- Introduction to IoT Security

- Asynchronous Design Practices for Secure Hardware

- Introduction to Hardware

Security and Trust

- Secure Architecture Design

- Physical Inspection

- Hardware Security Lab

- Advanced Topics in Hardware Security and Trust

- Physical Inspection

- Introduction to AMS Security

15

## Workforce Development Application Engineer Training & Technical Transition

## Praveen CHAWLA

PRESIDENT/CTO

EDAPTIVE COMPUTING, INC.

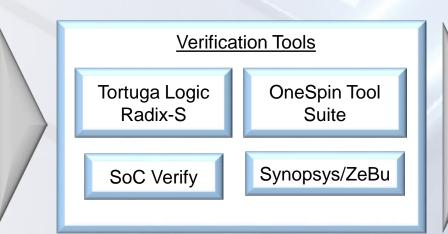

#### Workforce Development Goals:

- Transition students and industry professionals into the hardware security workforce for government agencies, national laboratories and industry sectors

- Apply automation tools to ease transition and increase efficiency of workforce entry into verification engineering for assuring and securing microelectronics

#### Workforce Development Architecture:

Holistic and integrated approach to both train the next generation of hardware security engineers and develop comprehensive, enterprise tools and solutions for assured and secure microelectronics

#### **Application Engineer Training:**

Assured & Secure Microelectronics

#### **Technical Transition:**

|      | University of Florida:                                                                          | University of Cincinnati:                                                                                                                                | Edaptive Computing:                                                                                                     | DARPA IDEA/POSH:                                                                                        |

|------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

|      | <ul> <li>FICS SoC Trust &amp; Validation<br/>(STV)</li> <li>FICS AutoBOM – Automatic</li> </ul> | <ul> <li>Memometer – Generation and interrogation of a digital signature of an FPGA/ASIC/PLD</li> <li>FACETS – Formal Assertions and Security</li> </ul> | <ul> <li>SoC Verify – Enterprise         Verification Management     </li> <li>Synopsys Emulation accessible</li> </ul> | <ul> <li>Support ZS3 Emulation</li> <li>University of Michigan</li> <li>Princeton University</li> </ul> |

| Dist | Bill of Materials for PCB ribution A: Approved for Public Release; Distri                       | Monitoring for Trusted SoCs                                                                                                                              | and enabled through cloud                                                                                               | Washington University                                                                                   |

#### **Current Workforce Training Numbers:**

| Active Accounts on TSS: | OneSpin Trainees: | Radix-S Trainees: | Synopsys Tools Trainees: |

|-------------------------|-------------------|-------------------|--------------------------|

| 108                     | 96                | 24                | 17                       |

#### **Current 2020 OneSpin Training Schedule:**

| Class:                            | Date:                                        |  |

|-----------------------------------|----------------------------------------------|--|

| Online OneSpin EC Course          | August 5th                                   |  |

| Online OneSpin FIA/FPA Course     | August 19 <sup>th</sup>                      |  |

| Online OneSpin 360 DV Apps Course | September 9 <sup>th</sup>                    |  |

| Online OneSpin ABV & MDV Course   | October 7 <sup>th</sup>                      |  |

| Online OneSpin EC Course          | October 28 <sup>th</sup>                     |  |

| Online OneSpin 360 DV Apps Course | November 4 <sup>th</sup>                     |  |

| Online OneSpin FIA/FPA Course     | November 18 <sup>th</sup>                    |  |

| OneSpin 3-Day Intro Course (ECI)  | December 15 <sup>th</sup> – 17 <sup>th</sup> |  |

#### Online Tortuga Logic Radix-S Training Class:

- 1st Class: July 2020

- Additional Classes: September-October 2020

#### OneSpin/ECI Formal Verification Certification Intro Training Class

- September 2020

- Synopsys Verdi and ZS Platform Training

- Fall 2020

#### **Success Checks:**

**Training Program Certification**

Track Student Training

Attendance

Tool Usage in Cloud Environment

**Technical Support Services**

## For Education & Workforce Development Panel: Centauri Educational **Outreach and Partnerships**

## Cheyanne HARSHMAN

**CENTAURI**WORKFORCE DEVELOPMENT LEAD

#### **University Engagement**

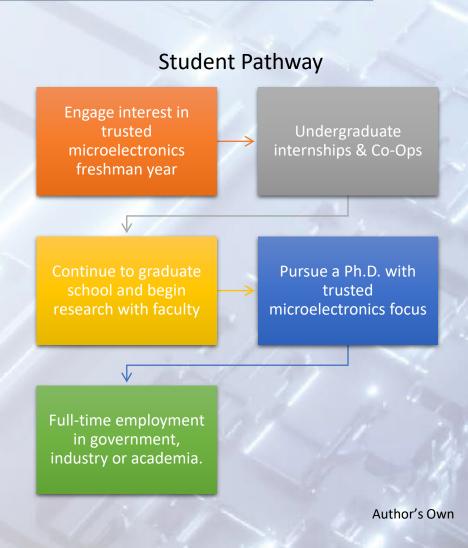

- Centauri is focused on creating a national approach to interacting with universities and additional academic institutions to engage undergraduate, graduate, and Ph.D students in collaboration with faculty members to promote and foster interest and skills in trusted and assured microelectronics through:

- Internships

- Co-Ops

- Employment

- Faculty Research

- Student mentorship/collaboration

- Onsite visibility

- Develop long term partnerships with universities to create self-sustaining pipeline

- Topics developed include microelectronic design, fabrication, logistics, testing, and analysis.

#### Military Academies and Institutions

- Increase Military members with Degrees

- Improve AFIT/NPS research quality

- Improve pipelines for military students to civilian schools

- Targeted Short Courses

- Knowledge and skill development for the DoD workforce involved in design, fab, logistics, testing, analysis, and assurance techniques.

- Proposed Trust in Microelectronics Ph.D. program

- For the students to understand the synergistic nature of the many aspects of microelectronics trust and to be able

to develop solutions to both current and future challenges to the security of the microelectronics environment.

- Key areas of knowledge include:

- Electronics architecture and manufacturing

- Test and Evaluation of microelectronics

- Supply Chain management

- Systems Engineering management

- Complex Systems analysis

- Two students at Air Force Institute of Technology (AFIT)

- Two students at Navy Postgraduate School (NPS)

#### **Thank You**

## Questions?

Education & Workforce Development Panel: SCALE (Scalable Asymmetric Lifecycle Engagement)

## Peter BERMEL

SCALE PRINCIPAL INVESTIGATOR

ASSOCIATE PROFESSOR OF ELECTRICAL

& COMPUTER ENGINEERING

PURDUE UNIVERSITY

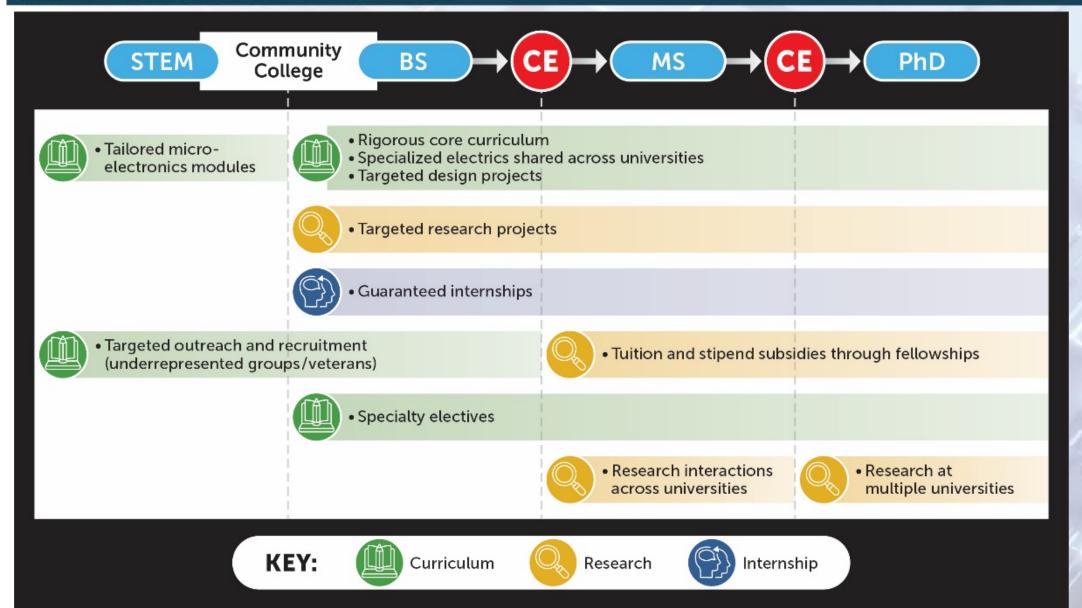

## SCALE provides the US with an asymmetric workforce advantage in microelectronics

- To motivate talented STEM undergraduate and graduate students to choose DOD/GOV/DIB employment

- For DOD/GOV/DIB to identify and hire new employees

**University Faculty, Staff, Graduate Student Mentors**

- Train students and support faculty in specific technical areas:

- Radiation-hardening

- Heterogeneous integration

- System-on-Chip

- Scalable to multiple universities

- Replicable to additional topics important to the DOD/GOV/DIB

SCALE Microelectronics

Workforce PublicPrivate-Academic

Partnership

# SCALE rigorously develops key KSAs through courses, projects, research, and internships

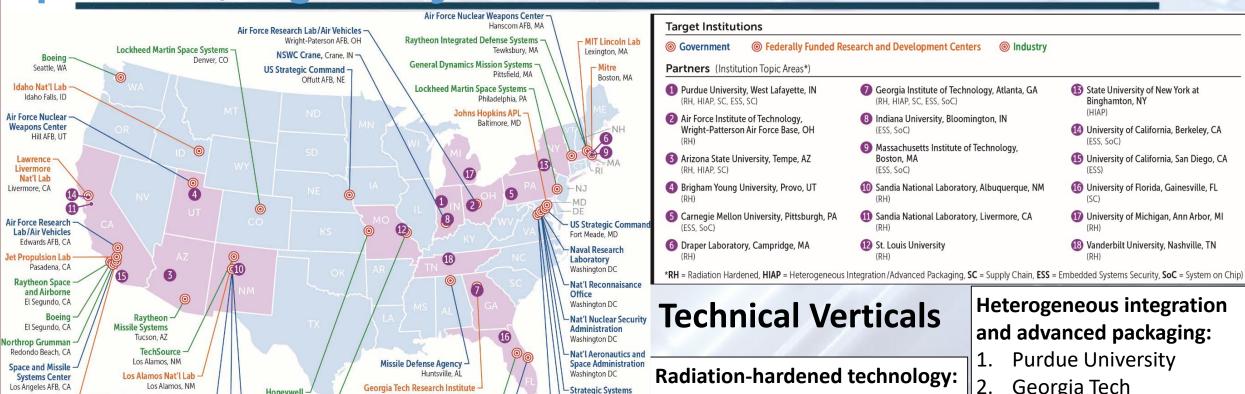

### SCALE is a nationally coordinated network of partners, regionally executed

Program

Washington DC

Fort Belyoir, VA

**Defense Threat**

Reduction Agency

#### **SCALE PPAP National Network**

Lockheed Martin Missiles and Fire Control

Air Force Technical Applications Center

US Nuclear and Chemical Agency -

Honeywell

Boeing, St. Louis, MO

Kansas City, MO

- Vanderbilt

- Air Force Institute of **Technology**

- St. Louis University

- **Brigham Young University**

- **Arizona State University**

- Georgia Tech

- **Purdue University**

- Georgia Tech

- **SUNY-Binghamton**

- **Arizona State University**

#### System on Chip:

- **Ohio State University**

- Georgia Tech

- Purdue University

- **UC-Berkeley**

Air Force Nuclear Weapons Center

Air Force Research Lab/Space Vehicles -

Kirtland AFB, NM

Nat'l Nuclear Security Administration

Aerospace Corp

Los Angeles, CA

### Carolyn GOERNER

CLINICAL PROFESSOR OF MANAGEMENT KELLEY SCHOOL OF BUSINESS, INDIANA UNIVERSITY-BLOOMINGTON

### **Best Practices in Talent Management**

- Recruiting/Selection

- Realistic Job Previews (RJPs)

- Long-term relationships

- "Success Profiles"

- Performance Management

- Regular feedback cycles (vs. annual reviews)

- Customized, goal-driven assessments

- Coaching

### **Best Practices in Talent Management**

Emphasize company culture

Rapid Talent Allocation

Psychologically safe work environment

### **Thank You**

# Questions and Open Panel Discussion

# T&AM: Create a Robust and Resilient Microelectronics Pipeline Panel Agenda

- 1415 1435 Introduction

- Dr. Matthew Casto, T&AM Program Director

- 1425 1600 Education and Workforce Development Consortium Panel

- Allison Smith, Naval Surface

Weapons Center Crane, T&AM

Technical Execution Lead

- Panel Members NSS IECRC,

Universities Cincinnati, Purdue,

Florida and Ohio

- 1600 1615 AFTERNOON BREAK

- 1615 1645 OSD and AF Microelectronics Design and Prototype Challenge

- Vipul J. Patel, AFRL, Sr. ElectronicsEngineer

- 1645 1715 Technology Development

- Peter O'Donnell, Army Combat Capabilities Combat Command, T&AM Technical Execution Area

- 1715 1745 Supply Chain Awareness and Security

- Adam Hauch, Naval Surface

Weapons Center Crane, Technical

Execution Area Lead

- 1745 1845 Virtual Demo & Poster Session

# T&AM: Create a Robust and Resilient Microelectronics Pipeline Panel Agenda

- 1415 1435 Introduction

- Dr. Matthew Casto, T&AM Program Director

- 1425 1600 Education and Workforce Development Consortium Panel

- Allison Smith, Naval Surface

Weapons Center Crane, T&AM

Technical Execution Lead

- Panel Members NSS IECRC,

Universities Cincinnati, Purdue,

Florida and Ohio

- 1600 1615 AFTERNOON BREAK

- 1615 1645 OSD and AF Microelectronics Design and Prototype Challenge

- Vipul J. Patel, AFRL, Sr. ElectronicsEngineer

- 1645 1715 Technology Development

- Peter O'Donnell, Army Combat Capabilities Combat Command, T&AM Technical Execution Area

- 1715 1745 Supply Chain Awareness and Security

- Adam Hauch, Naval Surface

Weapons Center Crane, Technical

Execution Area Lead

- 1745 1845 Virtual Demo & Poster Session

#### **CLEARED**For Open Publication

Jul 30, 2020

SLIDES ONLY

NO SCRIPT PROVIDED

Department of Defense

OFFICE OF PREPUBLICATION AND SECURITY REVIEW

# Trusted and Assured Microelectronics (T&AM) Technology Development Technical Execution Area (TEA)

Peter O'Donnell

Army Combat Capabilities Development Command Aviation & Missile Center (CCDC AvMC)

DARPA Electronics Resurgence Initiative (ERI)

August 19, 2020

#### **Technology Development TEA Overview**

### Develop a pipeline of robust and resilient microelectronics technologies that are vital to U.S. battlefield advantage and critical to U.S. infrastructure

- Leverages State-Of-The-Art (SOTA) commercial technology to co-develop assured solutions

- Adapts SOTA commercial technology to enable Department of Defense (DoD) unique solutions

- Accelerates development of SOTA technology enabling earlier adoption into DoD Programs with lower risk

- Compute Platforms

- Domain Specific Technologies

- Programmable Logic

- Supply Chain Solutions

- Enables rapid acquisition and deployment of SOTA commercial microelectronics

- Early access to technology enables modernized warfighting capability

- SOTA Requirements and Market Pull enabling Assurance & Security Tech Insertion

#### **Technology Development TEA Overview**

#### <u>Inputs</u>

DoD Programs & Program Executive Offices (PEOs)

T&AM Broad Agency Announcement

T&AM

Technical

Execution

Areas (TEAs)

Industry Engagement

Disruptive Technology Threat Information

DARPA ERI

#### **Technology Development**

Size, Weight, and Power (SWaP) / Performance

**Industry**

Government

Compute Platforms

- High Performance

- Artificial Intelligence

- Board Consortium

Programmable Logic

- Field Programmable Gate Array (FPGA)

- Embedded FPGA (eFPGA)

Access / Availability Obsolescence

Security

DoD Unique Specialization Design & Integration

Commercial Off the Shelf (COTS) Co-Development

Supply Chain Solutions

Traceability

Assurance / Protection

> Domain Specific Technologies

- 5G / Communications

- Positioning, Navigation, and Timing (PNT)

- Autonomy

#### Results

Tech early access

Risk buy down / Tech Maturation

Transition & Partnerships

Economic Competitiveness

Ecosystem of DoD Solutions

#### **Technology Development TEA Overview**

Develop a pipeline of robust and resilient microelectronics technologies that are vital to U.S. battlefield advantage and critical to U.S. infrastructure

#### **Workshop Panelist:**

- 1. Peter O'Donnell T&AM Technical Execution Lead, Army CCDC, Protective **Technologies Division Chief**

- Thomas Dalrymple Technical Advisor, Sensor Subsystems, AFRL Sensors Directorate

- Sam Wanis, PhD Research Program Manager, Advanced Electronics, Northrop **Grumman Corporation**

- 4. Scott Suko Tech Subject Matter Expert, Northrop Grumman Corporation

- 5. Ryan Close, PhD (ST) Chief Scientist, Signal and Image Processing, C5ISR Center, Night Vision and Electronic Sensors Directorate (NVESD), U.S. Army Combat Capabilities Development Command (DEVCOM)

# T&AM: Create a Robust and Resilient Microelectronics Pipeline Panel Agenda

- 1415 1435 Introduction

- Dr. Matthew Casto, T&AM Program Director

- 1425 1600 Education and Workforce Development Consortium Panel

- Allison Smith, Naval Surface

Weapons Center Crane, T&AM

Technical Execution Lead

- Panel Members NSS IECRC,

Universities Cincinnati, Purdue,

Florida and Ohio

- 1600 1615 AFTERNOON BREAK

- 1615 1645 OSD and AF Microelectronics Design and Prototype Challenge

- Vipul J. Patel, AFRL, Sr. ElectronicsEngineer

- 1645 1715 Technology Development

- Peter O'Donnell, Army Combat Capabilities Combat Command, T&AM Technical Execution Area

- 1715 1745 Supply Chain Awareness and Security

- Adam Hauch, Naval Surface

Weapons Center Crane, Technical

Execution Area Lead

- 1745 1845 Virtual Demo & Poster Session

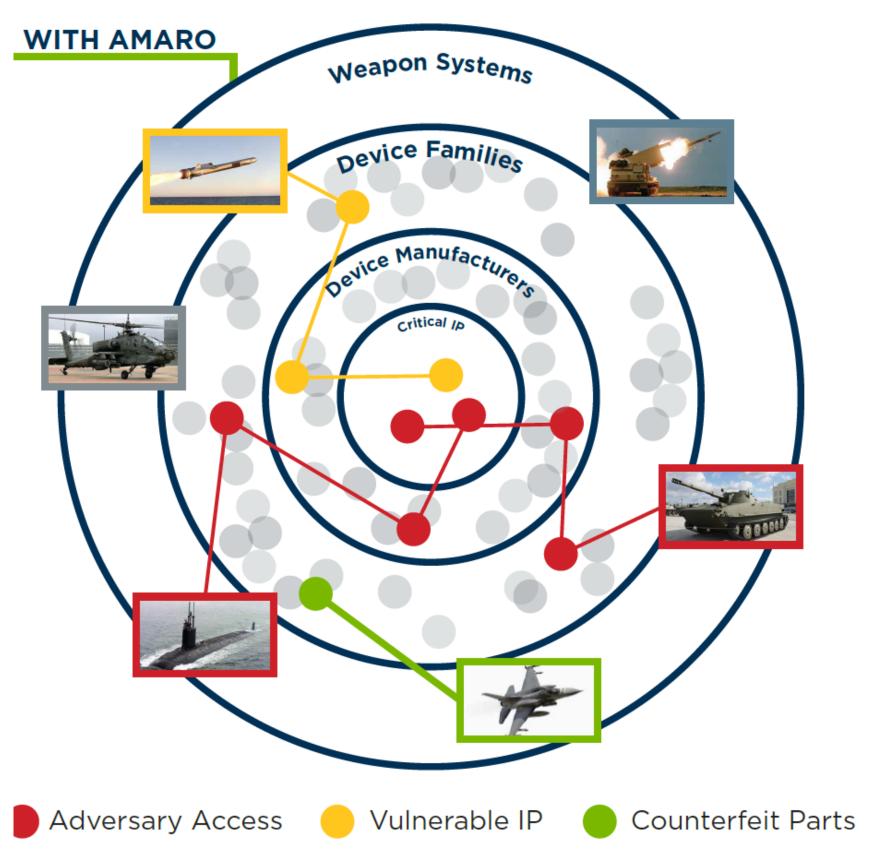

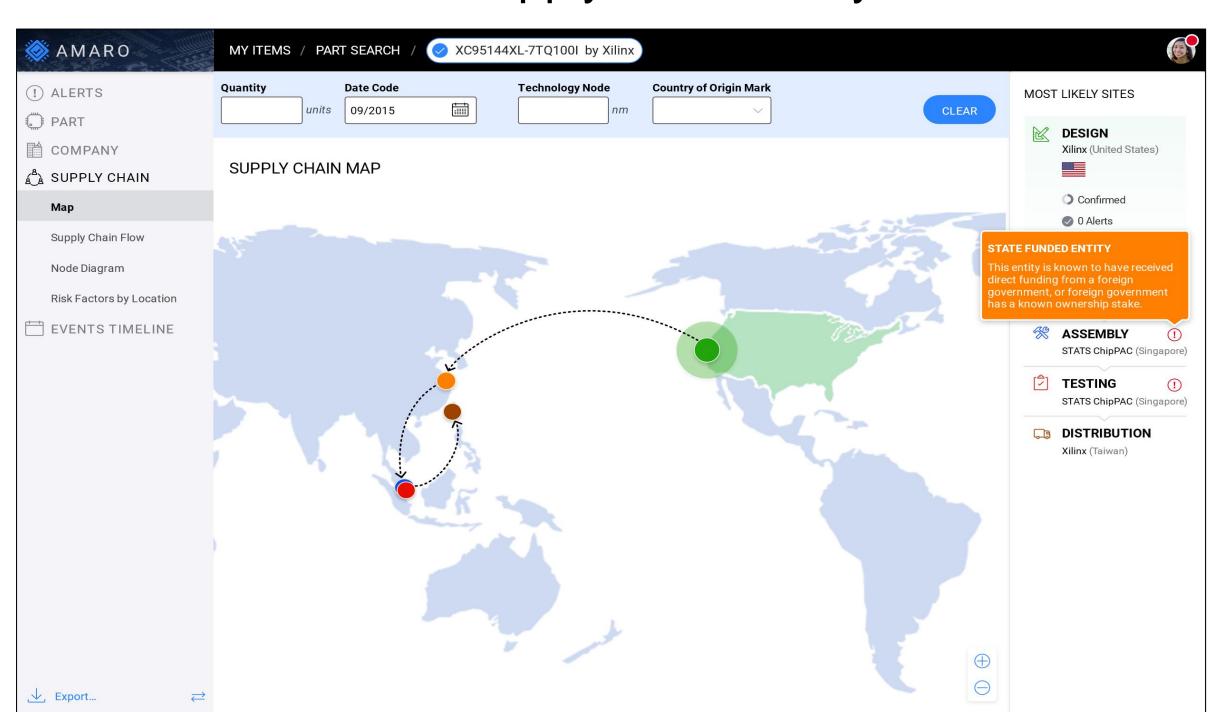

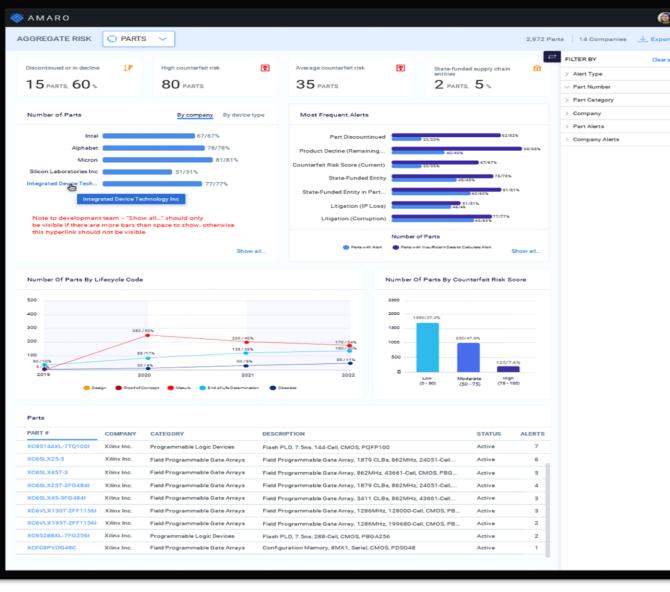

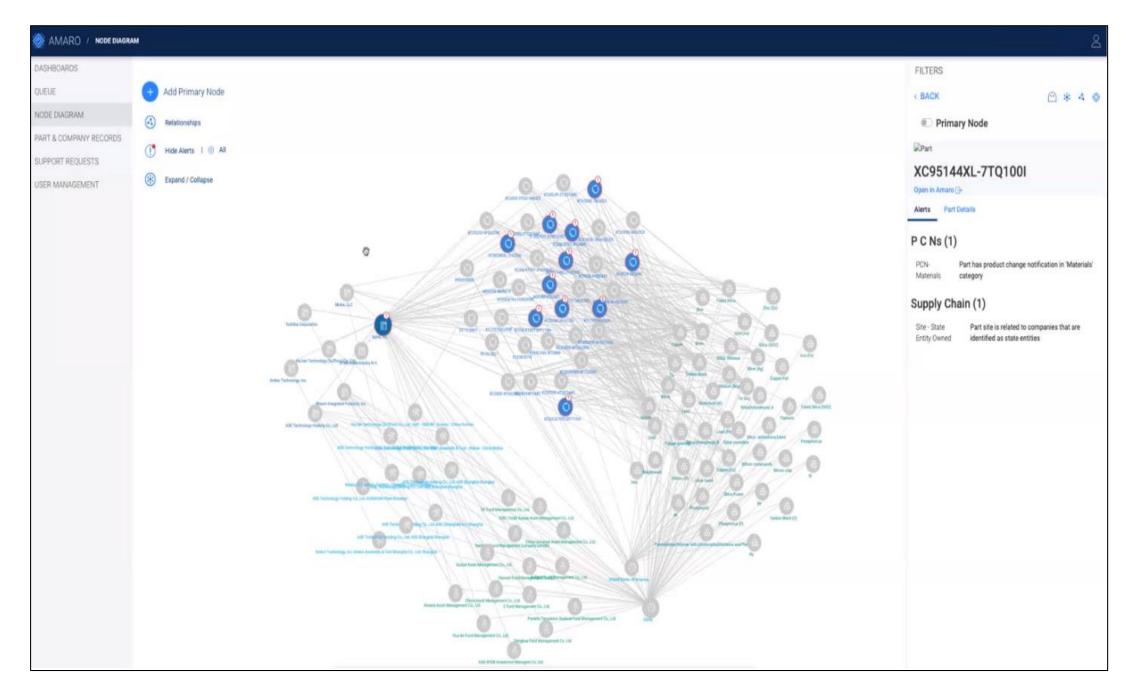

# **Automated Microelectronics Analysis and Reports Optimization Tool**

**NSWC Crane, KSM Consulting**

## AMARO

# T&AM Program/Supply Chain Awareness and Security

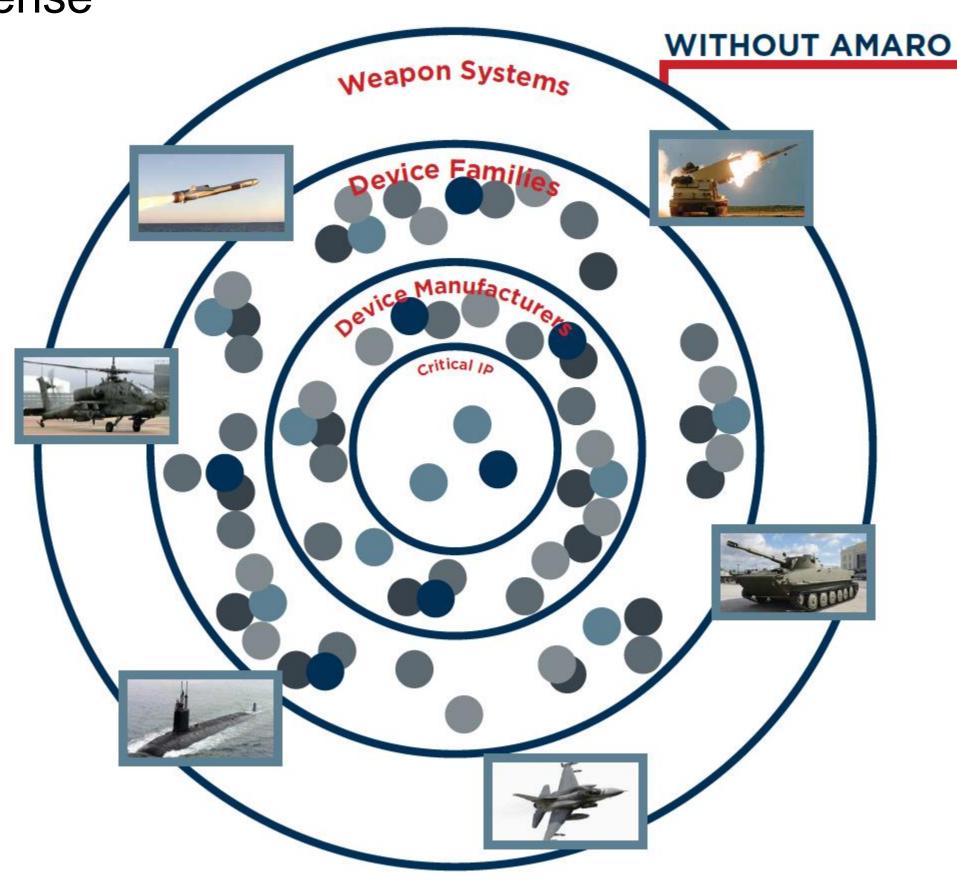

### The Challenge Today

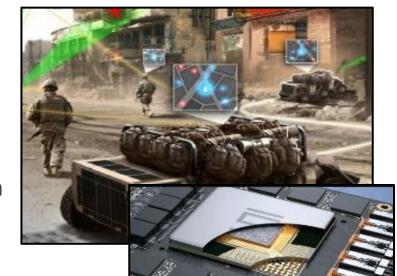

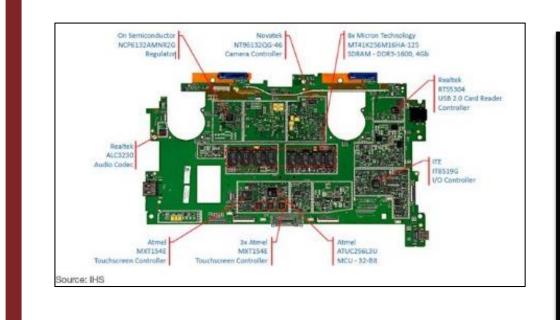

Supply chain tools on the market today only look at the risk of the overall manufacturer; which is insufficient for the needs of the Department of Defense

### Same company; different risk profiles for individual parts

Strategic analysis of microelectronics issues is a manual, time intensive process. The Department of Defense requires the capability to assess the fragility of the various semiconductor segments, and the ability to forecast the impacts of events like COVID-19, earthquakes, foundry closures, and acquisitions

### Solution

automates enhances and proactive identification of supply chain risk by digesting thousands of structured and unstructured government and nongovernment datasets, applying advanced analytics, and formulating easy-to-digest displays

### Strategic Analysis Capabilities

What parts are potentially impacted if the operations of specific sites are interrupted due to global events, such as the Carrier in the carr

Can we look across thousands of BOMs to identify an overreliance on specific suppliers or sites/locations?

Are there suppliers or supply chain sites that are owned or funded by a foreign government?

How can I track a threat or vulnerability through the supply chain to determine the impacted weapon systems?

What all parts in the DoD supply chain could be impacted if a trade war escalates with a foreign country?

## **AMARO** Capabilities

Part-Centric Supply Chain Analysis

Bill of Materials / Aggregate Risk Analysis

### Proactive Strategic Analysis Features

# DoD Research and Engineering Enterprise

Creating the Technologies of the Future Fight

**DoD Research and Engineering Enterprise**https://www.CTO.mil/

Twitter

@DoDCTO