ELECTRONICS RESURGENCE INITIATIVE

& MTO Symposium

ELECTRONICS RESURGENCE INITIATIVE

& MTO Symposium

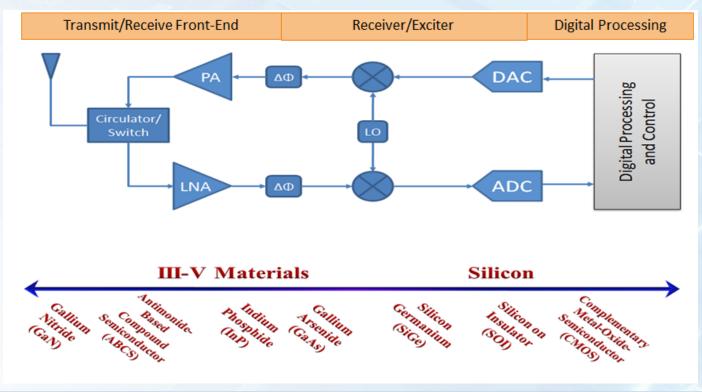

## MIXED-MODE GOVERNMENT APPLICATIONS AND NEEDS

# TONY QUACH CHRIS BOZADA

#### AIR FORCE RESEARCH LABORATORY SENSORS DIRECTORATE

#### HIGHLY INTEGRATED MICROSYSTEMS

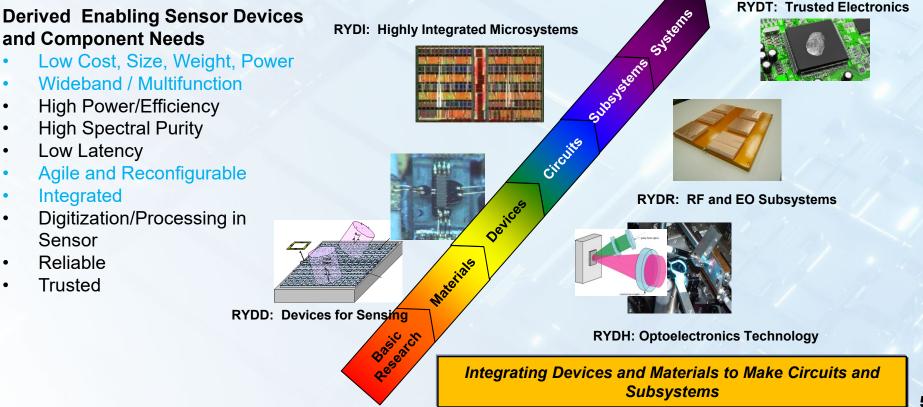

Mission: To discover, mature, and demonstrate emerging semiconductor and integration technologies that dramatically reduce the cost, size, weight, and power consumption of EO & RF sensor components to enable Air, Space, & Cyber Dominance!

#### **AEROSPACE SUBSYSTEMS & COMPONENTS DIVISION (AFRL/RYD)**

٠

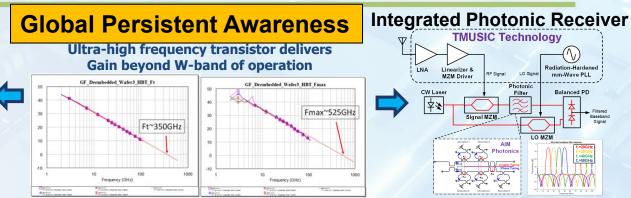

#### **Global Persistent Awareness**

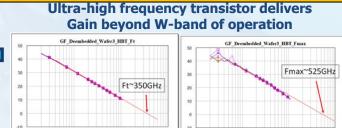

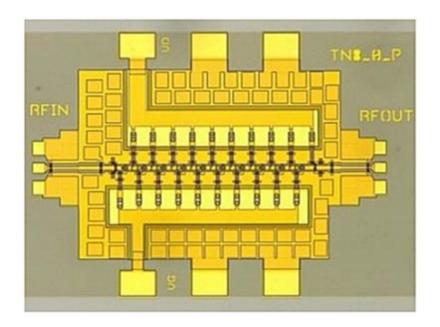

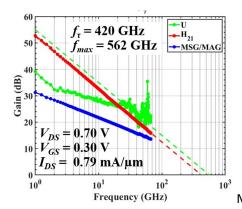

Ultra-high frequency transistor delivers Gain beyond W-band of operation

Phase 1 Measured Data

Frequency (GHz)

Contraction of the last

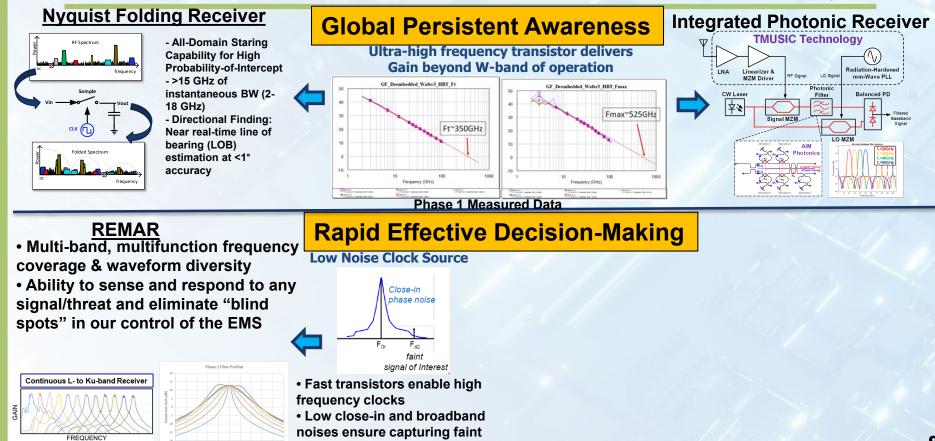

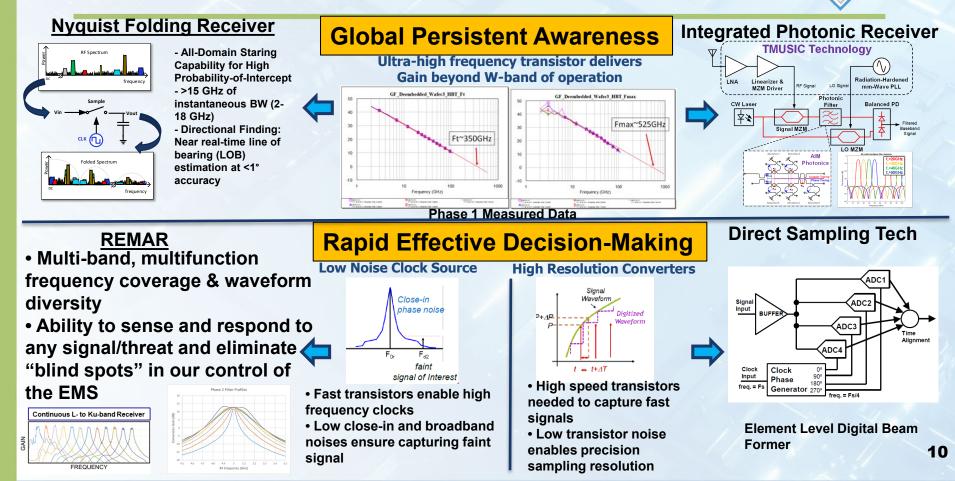

#### **Nyquist Folding Receiver**

- All-Domain Staring Capability for High Probability-of-Intercept ->15 GHz of instantaneous BW (2-18 GHz) - Directional Finding: Near real-time line of bearing (LOB) estimation at <1° accuracy

#### **Global Persistent Awareness**

Phase 1 Measured Data

100

Frequency (GHz)

1000

#### **Nyquist Folding Receiver**

- All-Domain Staring Capability for High Probability-of-Intercept - >15 GHz of instantaneous BW (2-18 GHz) - Directional Finding: Near real-time line of bearing (LOB) estimation at <1° accuracy

Phase 1 Measured Data

signal

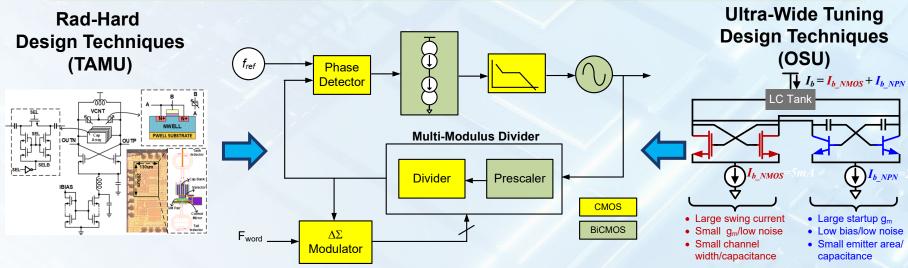

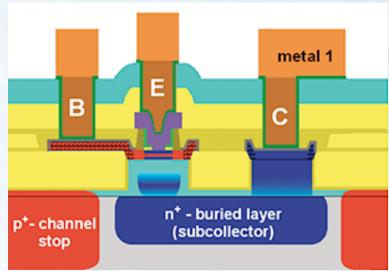

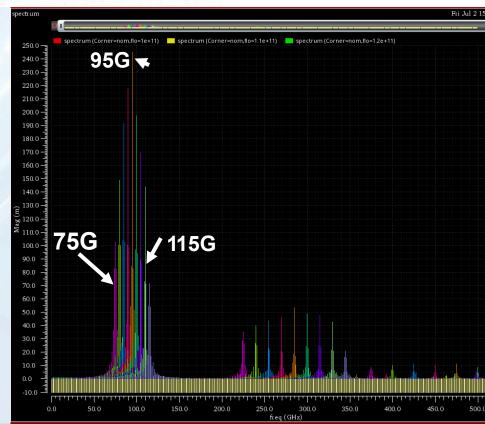

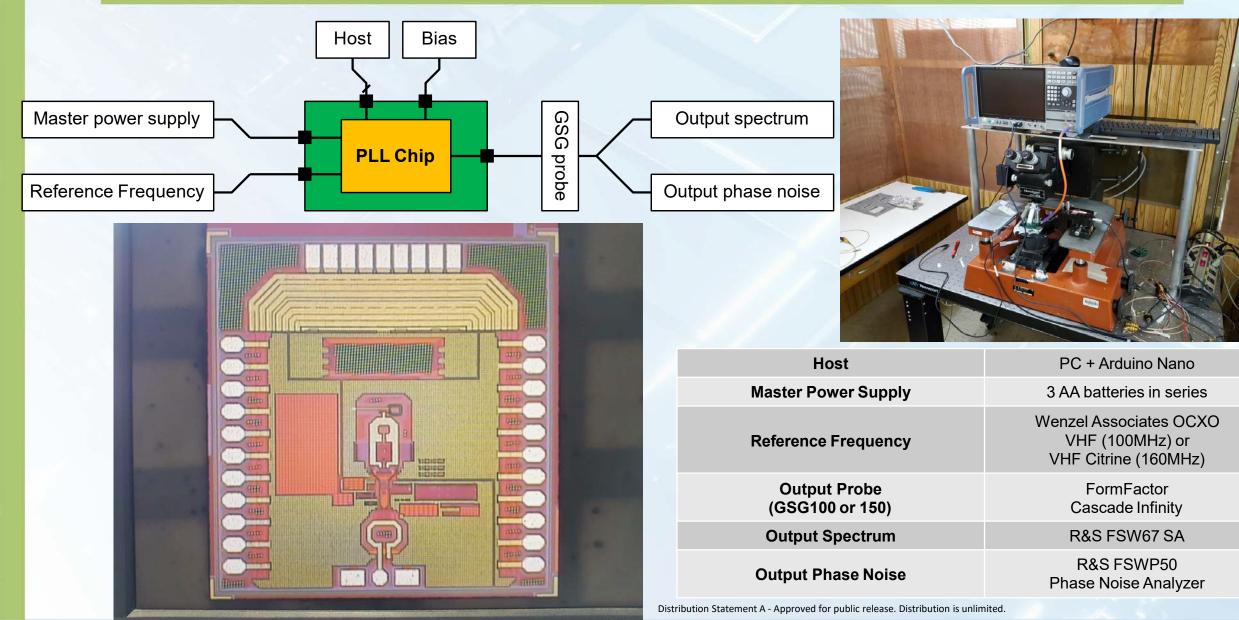

#### T-MUSIC TECHNOLOGY ENABLEMENT: RADIATION HARDEN, WIDE TUNING RANGE, MMW PLL

- Fast-switching CMOS and low 1/f noise BJT offer superior close-in noise performance in reference path

- BiCMOS VCO architecture exploits BJT's high  $g_m$  and low 1/f noise and CMOS's low thermal noise for wide TR and low phase noise at mm-Wave

- RHBD methodology employed for critical VCO components to provide rad tolerance while still meeting stringent performance specs

- DARPA T-MUSIC: Dr. James Wilson & Dr. Y.K. Chen

- Team Members: William Gouty, Steve Hary, Aji Mattamana, Dr. Samantha McDonnell, Lauren Pelan, & Dr. Paul Watson

- Collaborators:

- Dr. Waleed Khalil (Ohio State University)

- Dr. Samuel Palermo (Texas A&M University)

R ELECTRONICS RESURGENCE INITIATIVE S U M M I T

& MTO Symposium

ELECTRONICS RESURGENCE INITIATIVE

& MTO Symposium

# HYBRID MIXED-MODE ELECTRONIC CIRCUITS

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA).

The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

### **T-MUSIC UCLA TEAM**

C.K. Ken Yang

M.C. Frank Chang

#### Sudhakar Pamarti

- Graduate and Post-Doctoral Students:

- Chris Chen

- Allen Chien

- Avantika Singh

- Jiazhang Song

### **T-MUSIC GOALS**

- Benefits of SiGe HBT

- f<sub>T</sub> (f<sub>MAX</sub>)

- 1/f corner

- •

- g<sub>m</sub>/l<sub>c</sub>

- Dynamic range

- Program Goals

- Demonstration vehicles for ultra-high performance through hybrid design

|         | <u>Divider</u> | <u>PLL</u>       | <u>ADC</u>               |

|---------|----------------|------------------|--------------------------|

| Phase 1 | 100GHz         | -106dBc<br>@1MHz | 16b, 1GS/s,<br>500MHz    |

| Phase 2 | 200 GHz        | -120dBc          | 8b,<br>100GS/s,<br>50GHz |

- Benefits of CMOS

- Integration

- Fast switching

- Power

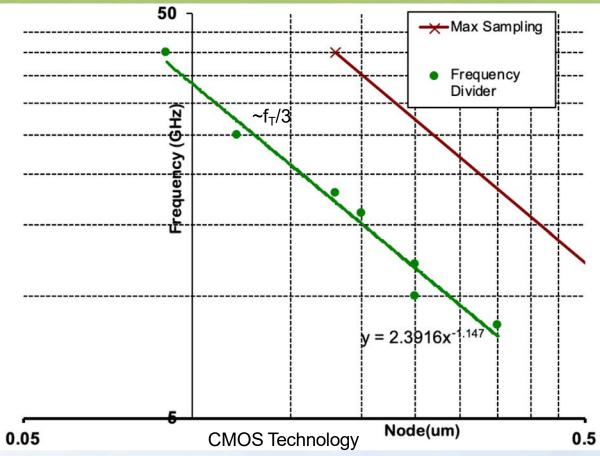

# FREQUENCY DIVIDER – LEVERAGE F<sub>T</sub>

- Maximum static divider frequency as a fraction of  $f_T$  ( $f_{MAX}$ ) is  $\sim f_T/3$ .

- Similar between HBT and CMOS

- Example: 200GHz on InP HBT (600GHz f<sub>T</sub>) [D'Amore]

- CMOS becomes very power hungry

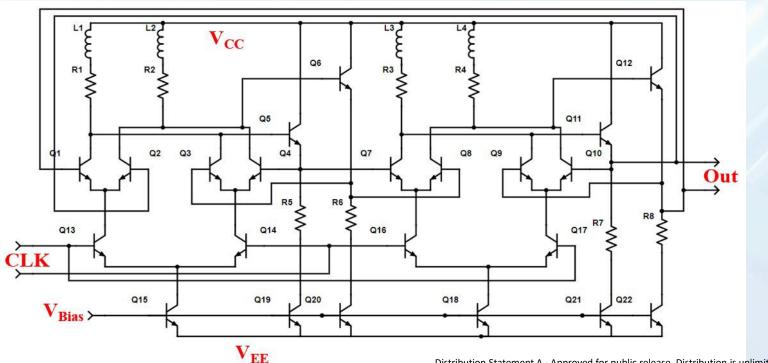

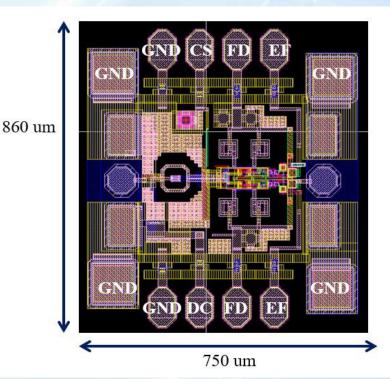

## **STATIC DIVIDER DESIGN**

**Design targets**

٠

- Broad frequency range

- Low input power, <-10dBm •

- Low total power, 66mW for main divider •

- Inductive peaking with EF buffering ۲

- Symmetric placement •

- Reduced wiring capacitors and more balanced delay.

(dBm)

Power

nput

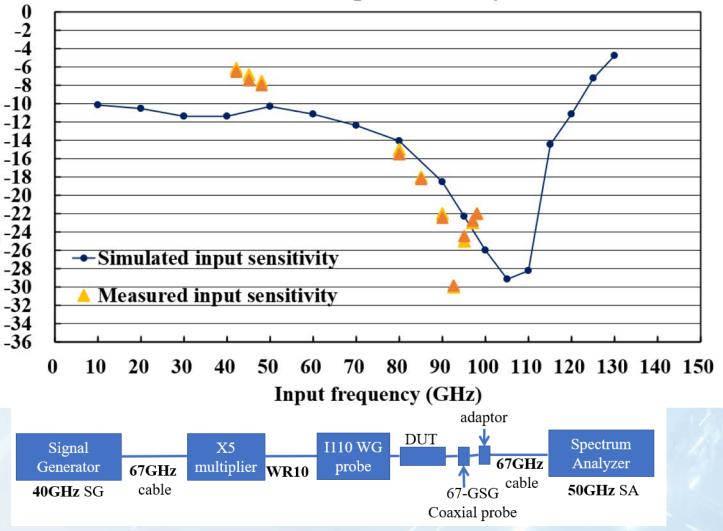

### **MEASUREMENT RESULTS**

- Sweeping input sensitivity

- The self resonant frequency is designed around 105-110 GHz, Measured at 100GHz

- The DC current is designed around 23 mA per stage – measured ~35mA

- Multiple test chips & repeatable yield.

- ATTEN 10dB -51.67d8m RL OdBm 1008/ PK SRCH 49.000GHz MARKER . MKR DELTA 49.000 GHz -51.67 dBm NEXT PEAK NEXT PK RIGHT NEXT PK LEFT HORE VBH 30 k H 2 SHP . Osec LOMA

Divider input sensitivity

## **DIVIDER PERFORMANCE COMPARISON**

| Technology<br>(Lg, f <sub>t</sub> /f <sub>max</sub> ) | Self-oscillating<br>frequency (GHz) | Max operating<br>frequency (GHz) | Minimum input<br>power (dBm) | DC power<br>(mW) | FoM<br>(GHz/mW) |

|-------------------------------------------------------|-------------------------------------|----------------------------------|------------------------------|------------------|-----------------|

|                                                       |                                     |                                  |                              |                  | FoM = SRF/DC    |

| 130nm, 240/330                                        | 70.34                               | >80                              | -49                          | 141              | 0.5             |

| 130nm, 250/330                                        | 64                                  | 92.5                             | -42                          | 56               | 1.14            |

| 180nm, 200/-                                          | 80                                  | 113                              | -30                          | 115              | 0.69            |

| 130nm, 300/500                                        | 111.6                               | 128.7                            | -20                          | 196              | 0.57            |

| 130nm, 200/250                                        | 75                                  | 90                               | -38                          | 61.6             | 1.22            |

| 160nm, 280/300+                                       | 92.5/89                             | 100/95                           | -39                          | 75.6/69.3        | 1.22/1.28       |

A. Awny, et al., "Design and Measurement Techniques for an 80 Gb/s 1-Tap Decision Feedback Equalizer," IEEE JSSC, vol. 49, no. 2, pp. 452-470, Feb. 2014.

V. Issakov, et al., "Low-voltage flip-flop-based frequency divider up to 92-GHz in 130-nm SiGe BiCMOS technology," 2017 INMMiC Workshop, Graz, 2017, pp. 1-3.

S. Trotta, et al., "A tunable flipflop-based frequency divider up to 113 GHz and a fully differential 77GHz push-push VCO in SiGe BiCMOS technology," 2009 IEEE RFIC Symposium, Boston, MA, 2009, pp. 47-50.

U. Ali, et al., "High speed static frequency divider design with 111.6 GHz self-oscillation frequency (SOF) in 0.13 µm SiGe BiCMOS technology," 2015 German Microwave Conference, Nuremberg, 2015, pp. 241-243.

P. Zhou, et al., "A low power, high sensitivity SiGe HBT static frequency divider up to 90 GHz for millimeter-wave application," in *China Communications*, vol. 16, no. 2, pp. 85-94, Feb. 2019.

#### Up to 120GHz is achievable in this technology!

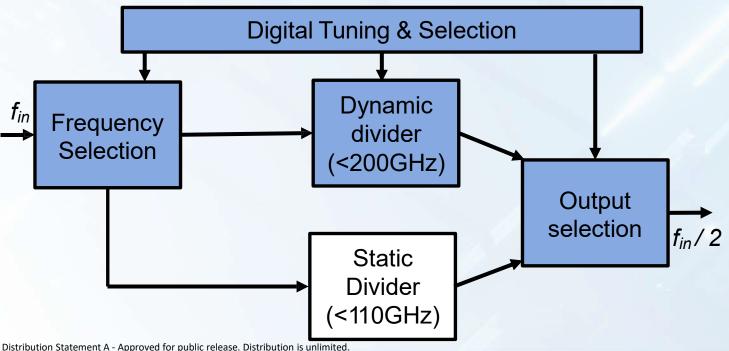

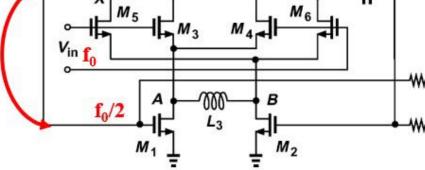

## **EXTENDING BEYOND F<sub>T</sub>/3**

- Tuned divider performance can exceed f<sub>MAX</sub>/2.

- Challenge #1 design a wide-range tuned-divider.

- Combining the two designs to improve range.

- Challenge #2 selection and detection of frequency setting

Vout

#### Injection to the bottom pair

$f_0/2$

C1

L2 3

VDD

Iref

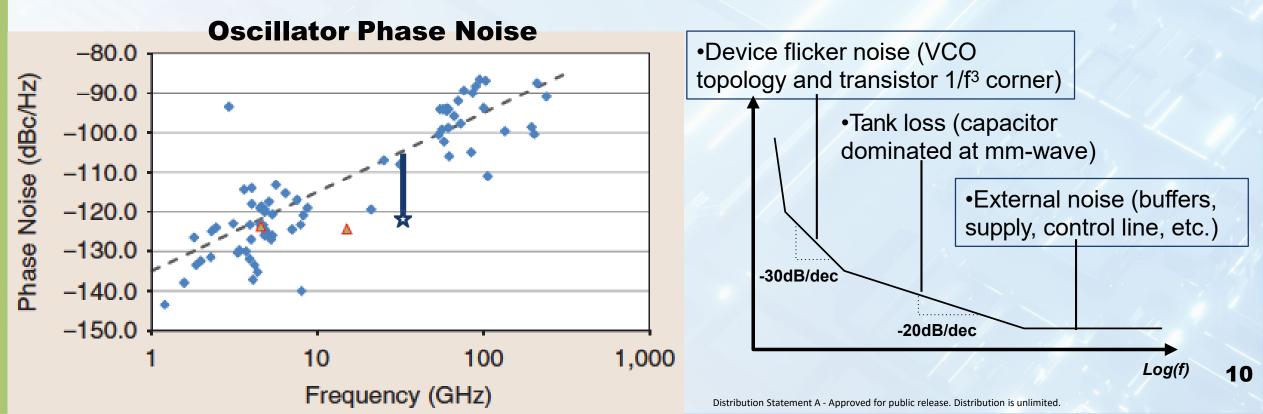

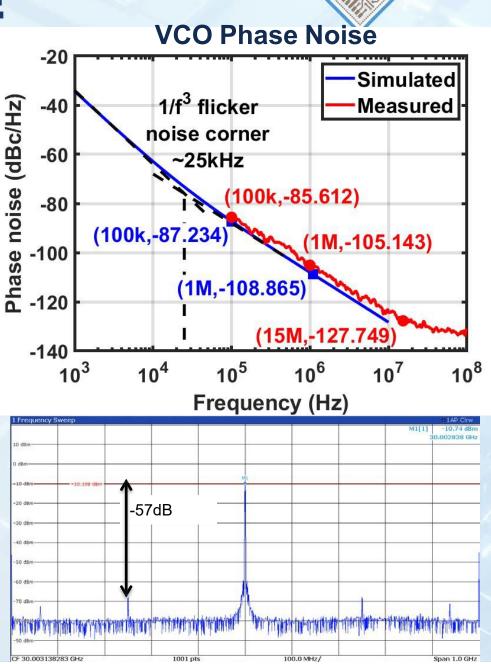

### MM-WAVE PLL – LEVERAGE 1/F, BUFFERING, AND CMOS SAMPLING

- PLL noise is largely from reference input and VCO.

- 100MHz crystal has sufficiently low phase noise 1MHz phase noise of 175dBc/Hz

- State of the art VCO equivalent noise at 30GHz is >-110dBc/Hz

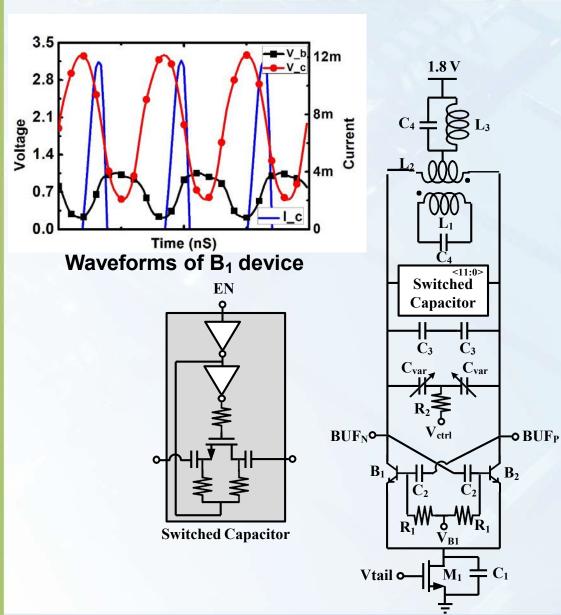

## **CLASS-C MULTI-HARMONIC RESONANCE VCO**

- SiGe

- High dynamic range

- Leverage high-f<sub>T</sub> device to achieve sufficient loop gain with minimum parasitic

- 1/f corner

- Drive capability for buffering

- CMOS

- Switched-C tuning

- Class-C operation

- Shrinks flicker noise region of operation by reducing zero-crossing time of the waveforms

- Saves DC power consumption

- Maintains high-Q tank by avoiding operating BJT in sat. region

- Multi-harmonic resonance

- Reduces up-converted flicker noise

- 2<sup>nd</sup> harmonic side-transformer

- $3^{rd}$  harmonic waveform shaping improves jitter and lowers  $P_{DC}$

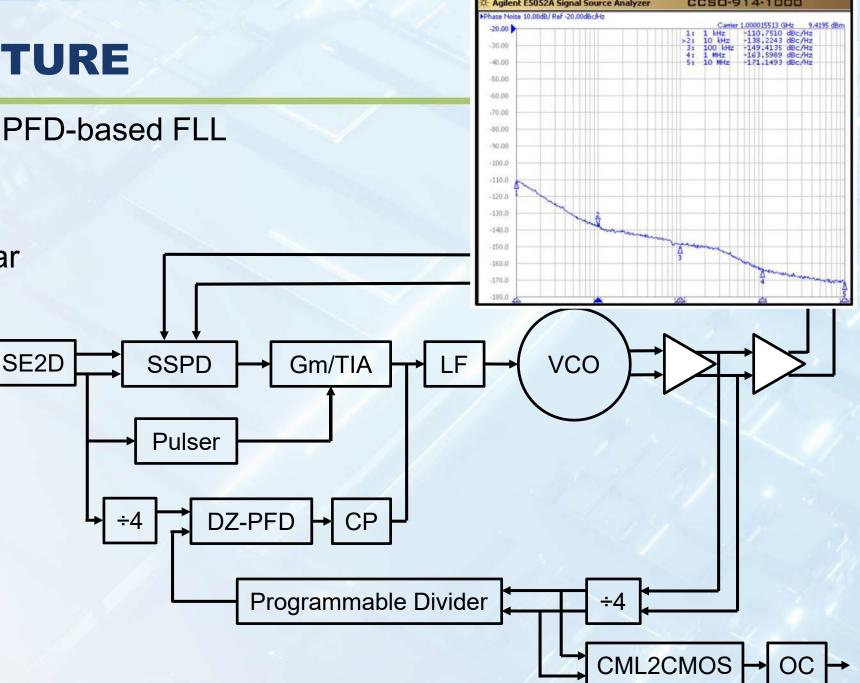

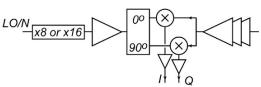

## PLL ARCHITECTURE

Direct sub-sampling + PFD-based FLL

**f**<sub>REF</sub>

- CMOS benefits

- Sub-sampling

- Low-power prescalar

- FLL components

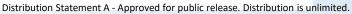

## **TEST CHIP IMPLEMENTATION**

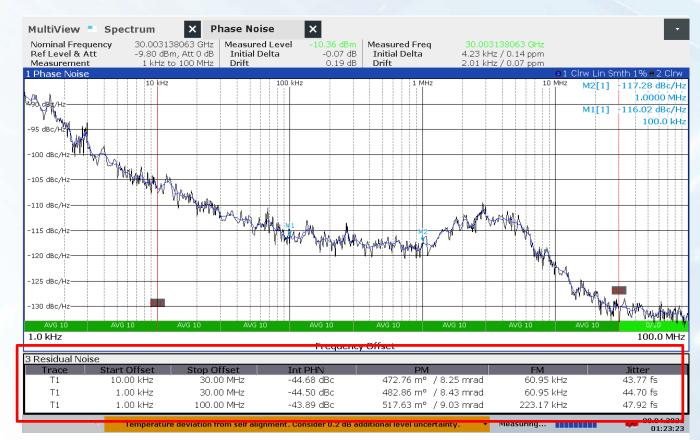

## **VCO AND PLL PERFORMANCE**

- PLL at 30GHz

- <50fs jitter</li>

- -117dBc/Hz @1MHz

- Reference spur level = -57dBc

Distribution Statement A - Approved for public release. Distribution is unlimited.

## **PERFORMANCE SUMMARY**

- PLL Performance Comparison

- Compared with other integer-N PLL at similar center frequency

|                                        | UCLA T-MUSIC          | ISSCC20 17.6              | ISSCC19 16.8        | ISSCC19 16.2               |

|----------------------------------------|-----------------------|---------------------------|---------------------|----------------------------|

| Technology                             | 0.18um<br>SiGe BiCMOS | 28nm<br>CMOS              | 65nm<br>CMOS        | 65nm<br>CMOS               |

| Technique                              | Sub-sampling<br>PLL   | Charge-Sharing<br>Locking | Sub-sampling<br>PLL | Sub-sampling PLL<br>+ ILFM |

| Ref. Freq (MHz)                        | 250                   | 250                       | 103                 | 100                        |

| Output Freq (GHz)                      | 27-30                 | 21.71-26.49               | 25.4-29.5           | 28-31                      |

| SPN 100kHz (dBc/Hz)                    | -112.23               | -103.8                    | -112.5              | -101.55                    |

| SPN 1MHz (dBc/Hz)                      | -114.85               | -110.4                    | -112.8              | -105.81                    |

| Jitter (fs)<br>(Integration range, Hz) | 43.77<br>(10k to 30M) |                           | 71<br>(1k to 100M)  | 76.4<br>(1k to 30M)        |

|                                        | 44.70<br>(1k to 30M)  | 75.89<br>(10k to 30M)     |                     |                            |

|                                        | 47.92<br>(1k to 100M) |                           |                     |                            |

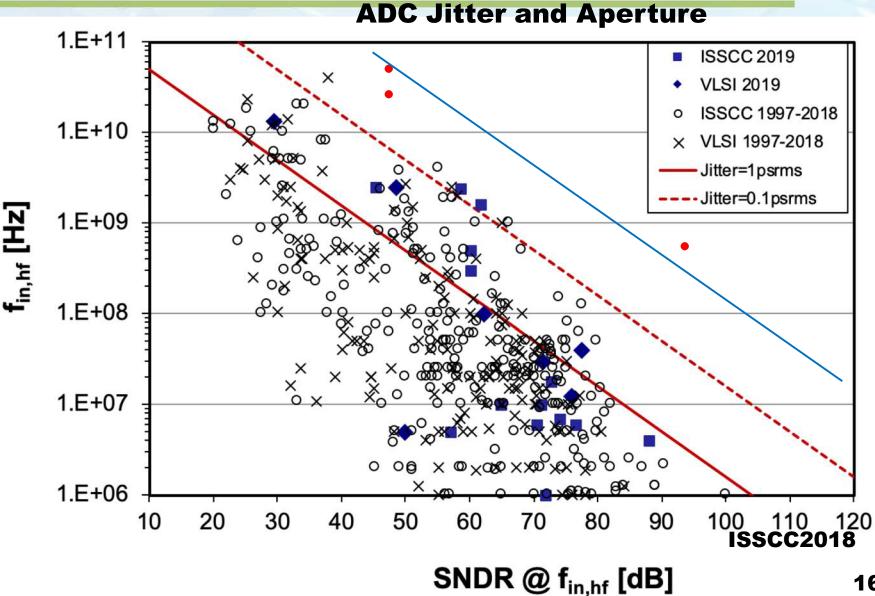

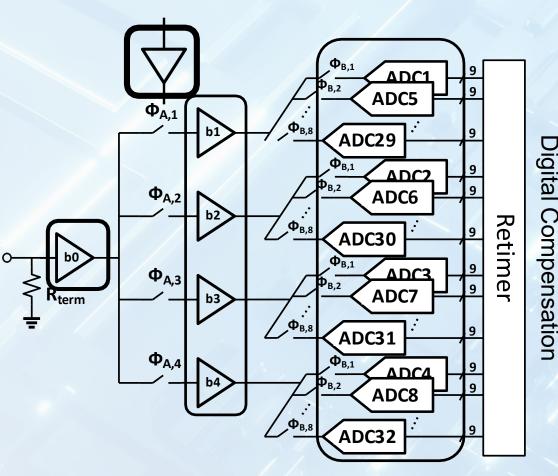

## **HIGH-PERFORMANCE ADC**

- Benefit of SiGe •

- Low jitter  $\bullet$

- Buffering ullet(power/noise)

- **Benefit of CMOS** ullet

- T/H and sampling

- Digital • linearization

## **INTERLEAVE-SAMPLING AND LINEARIZATION**

- Phase noise

- Leverage PLL performance

- Low noise buffering

- Digital compensation

- Accurate tuning of interleave paths makes design more challenging.

- Linearity

- Leverage high inherent linearity of buffers

- Digital compensation.

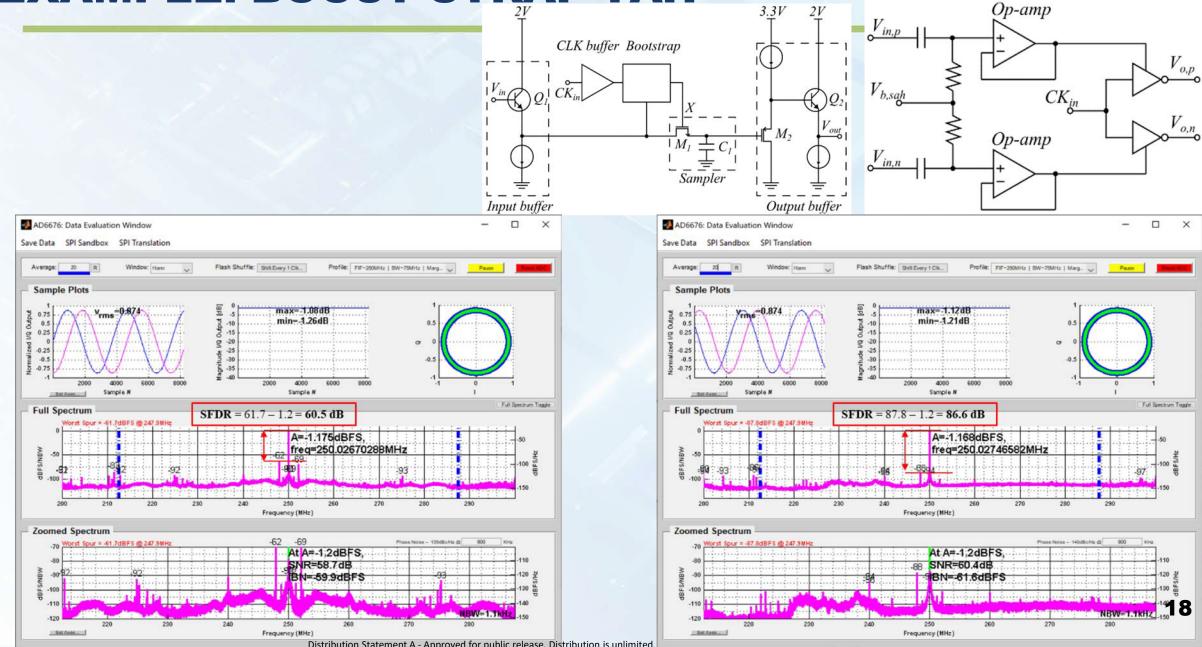

### **EXAMPLE: BOOST-STRAP TAH**

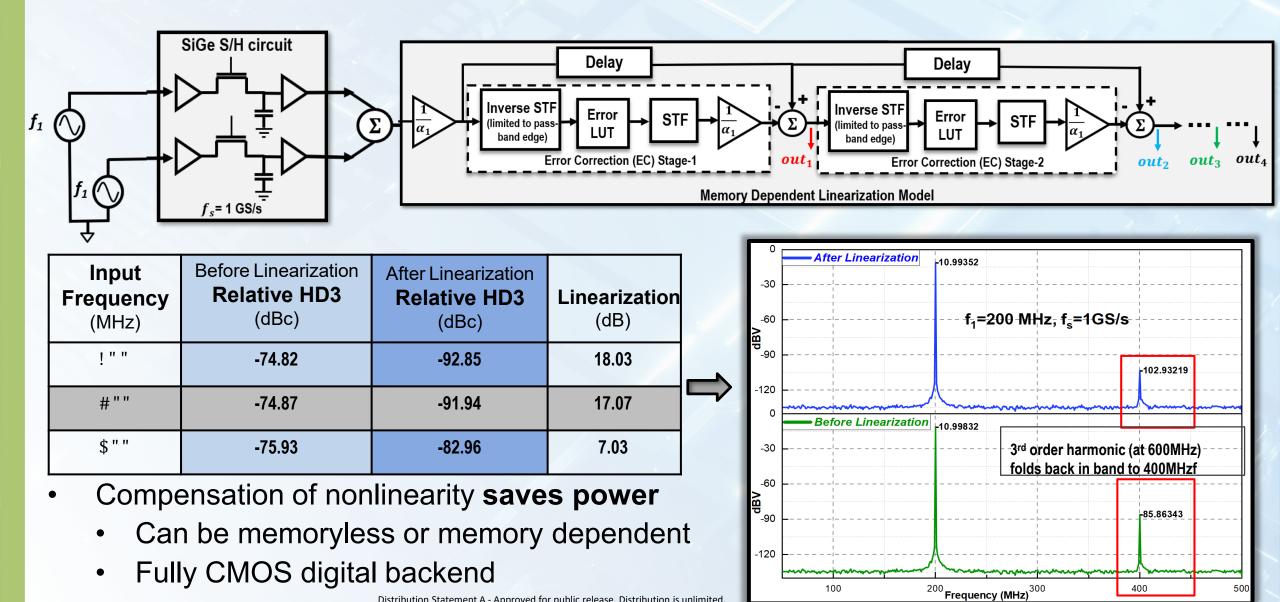

## **EXAMPLE: DIGITAL LINEARIZATION**

Distribution Statement A - Approved for public release. Distribution is unlimited.

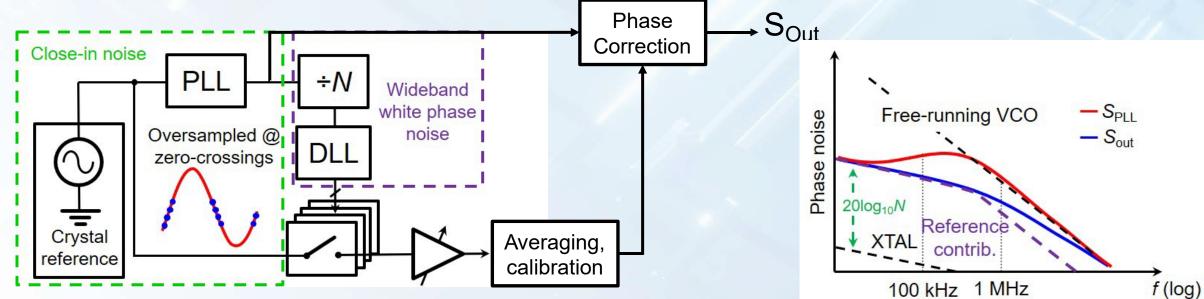

## **EXAMPLE: SAMPLING JITTER COMPENSATION**

- Reduce PLL jitter through feedforward phase noise cancellation

- Oversample clock jitter during rising/falling edges and correct using phase interpolators

- Enables wide bandwidth cancellation limiting factor in prior art

- Anticipated key building block performance

- ~200ps rise/fall times, ~10ps DLL resolution, 20 sampling points target 10fs rms

- Combine SiGe DLL to reduce wideband noise with CMOS calibration

- Same building blocks for digital **Spur Cancellation**

#### With the possibility of >500GHz $f_T$ and finFET CMOS!

#### The future of Hybrid Mixed-Signal Electronics is bright!

#### It opens up applications needing extreme performance.

R ELECTRONICS RESURGENCE INITIATIVE S U M M I T

& MTO Symposium

# QUESTIONS

#### Negative Capacitance Enabled Scaling to Achieve 1 THz Cut-off Frequency Transistors on a CMOS Platform

S. Salahuddin, UC Berkeley

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA).

The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

#### Negative Capacitance Enabled Scaling to Achieve 1 THz Cut-off Frequency Transistors on a CMOS Platform

S. Salahuddin, A. Niknejad, TJK Liu: UC Berkeley, S. Datta : Univ Notre Dame

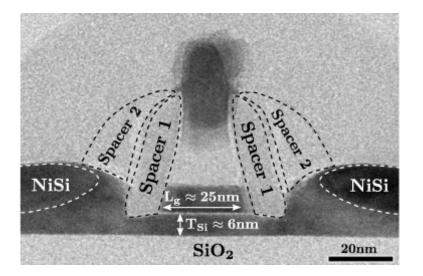

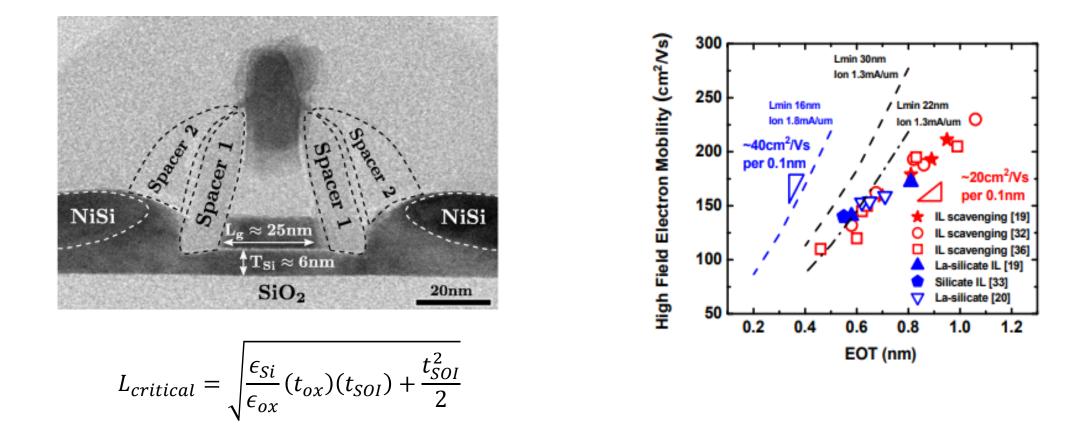

A typical FDSOI transistor

#### **Proposed Solution**

- Increase Cox without giving up mobility

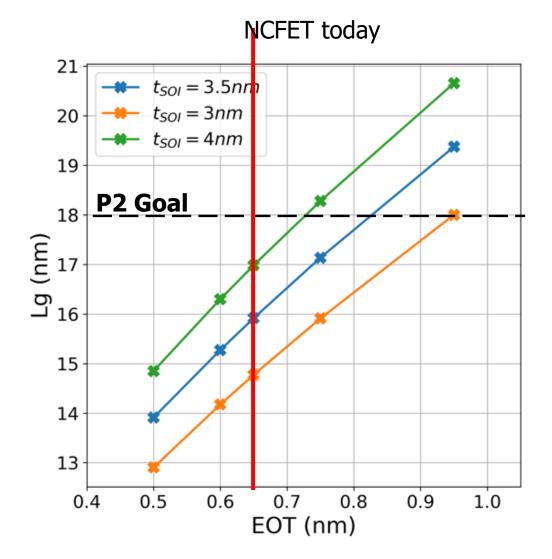

- i. to aid further scaling well below 20 nm

- ii. to reduce the effect of parasitic capacitance

- Reoptimize transistor structure for high frequency operation, e.g., by air gap spacers

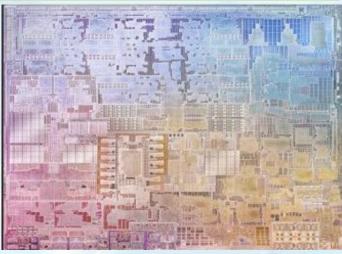

- Scaling is driven by the need to maximize the number of transistors achievable per unit area

- 3D structures bring in additional parasitic capacitance

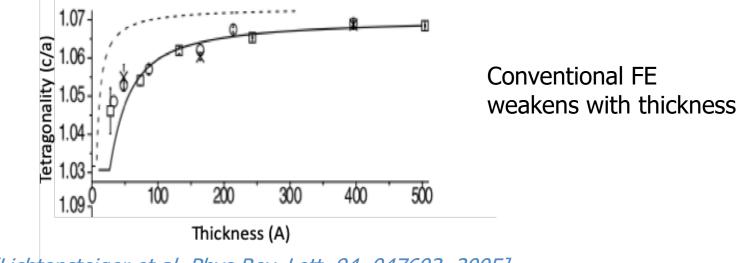

Conventionally lowering EOT using scavenging lowers mobility

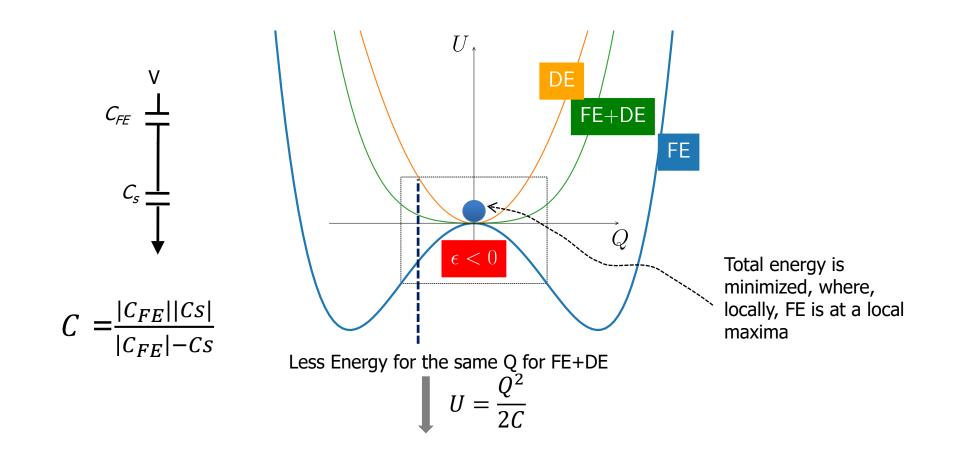

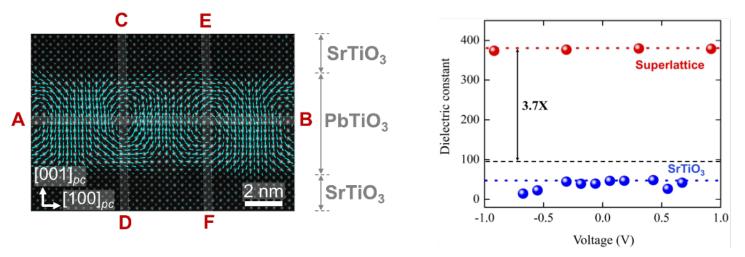

#### Exploiting Negative Capacitance

[Yadav et al Nature, 565, 7740, 468–471, 2019]

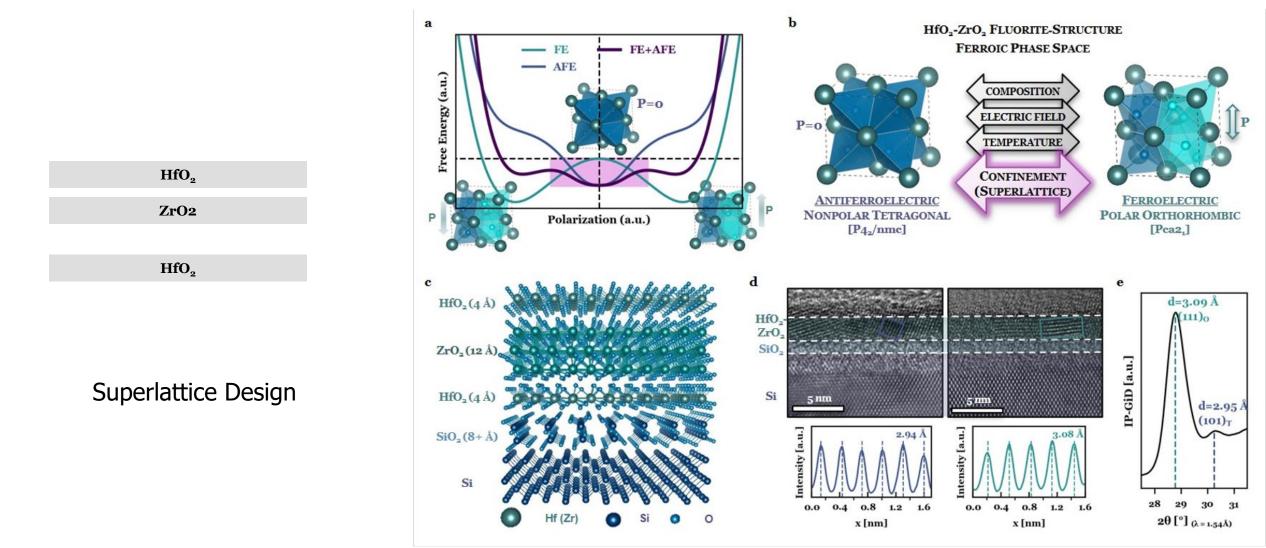

Superlattice Design

Material development: World's thinnest FE on Si

[Lichtensteiger et al, Phys Rev. Lett, 94, 047603, 2005]

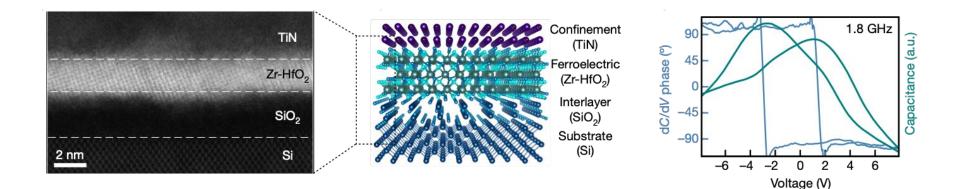

[S. Cheema et.al, *Nature* 580 (7804), 478-482, (2020)]

#### Superlattice Design

A mixed phase FE-AFE within just 1.8 nm

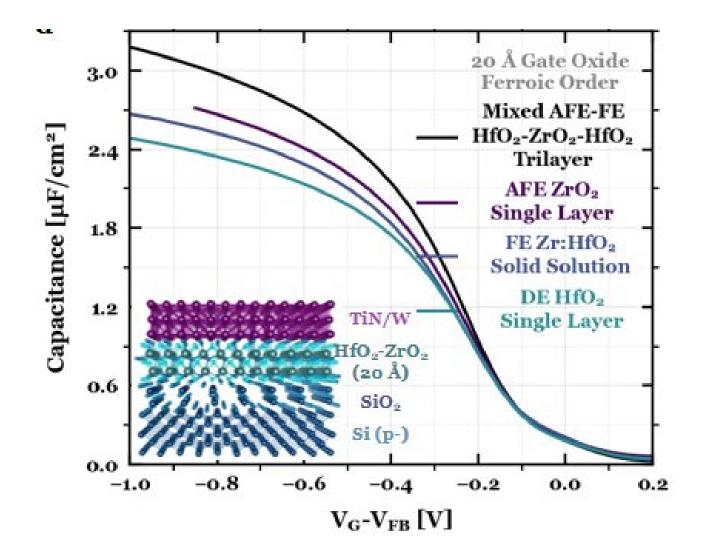

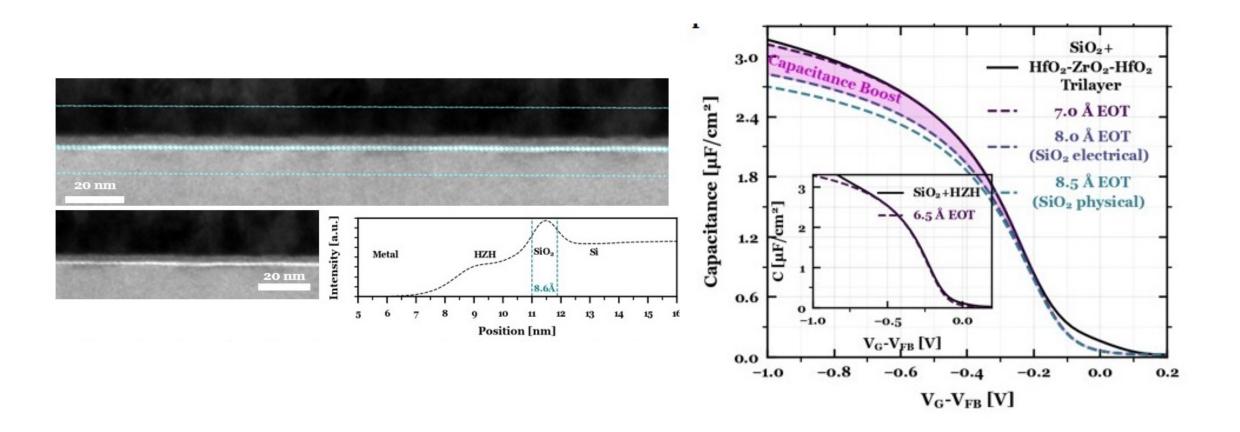

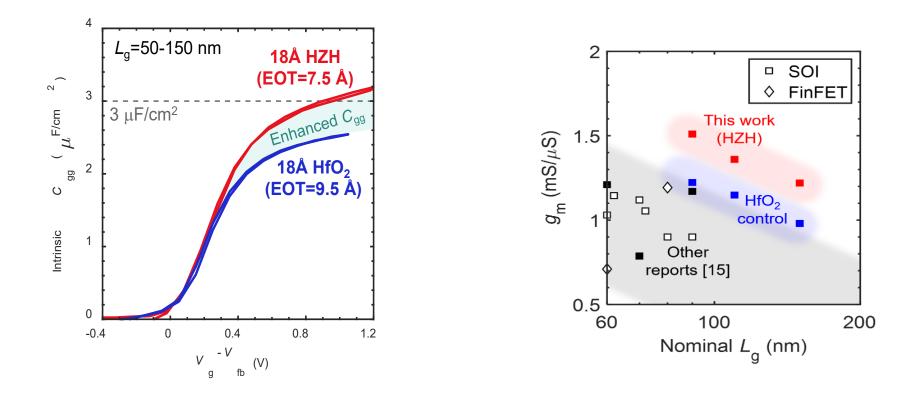

#### Capacitance Results

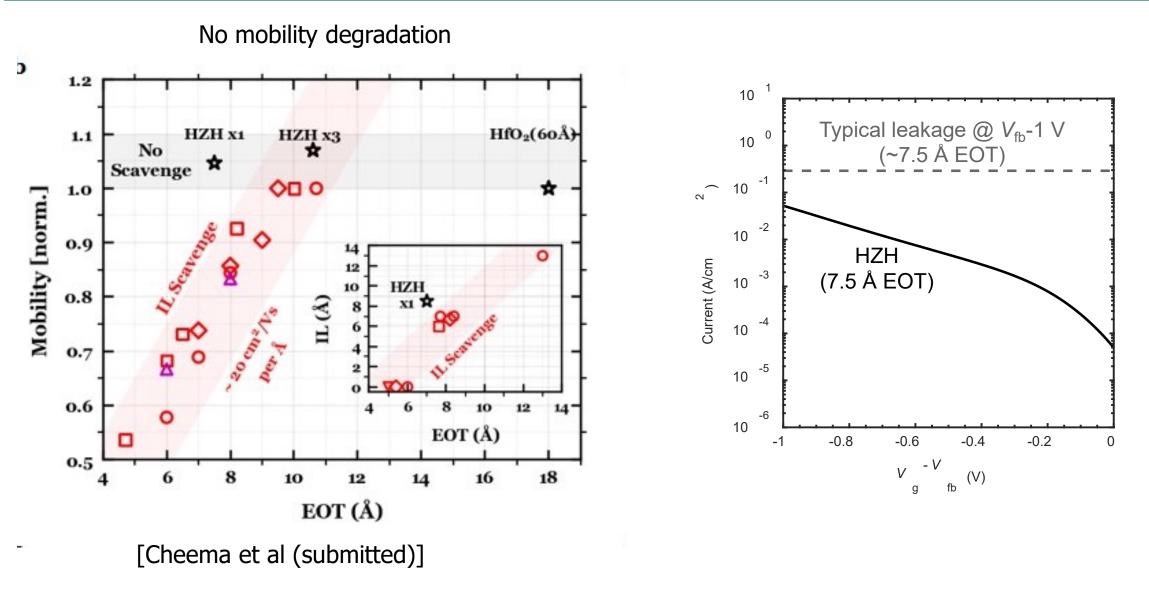

- Reaching EOT ranges that was not possible before without IL scavenging

- Mobility degradation is not present because IL has not been scavenged

#### Extracted from 25 GHz measurements

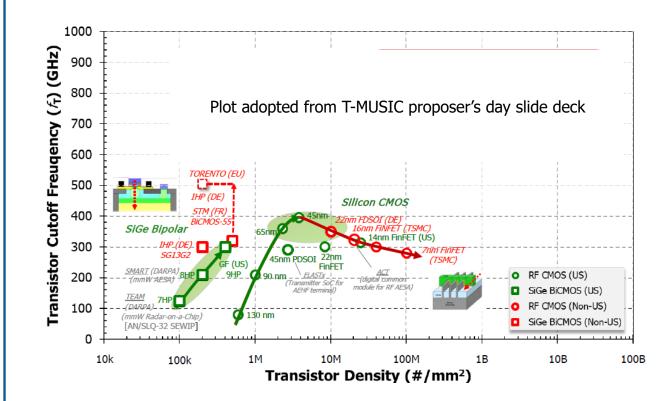

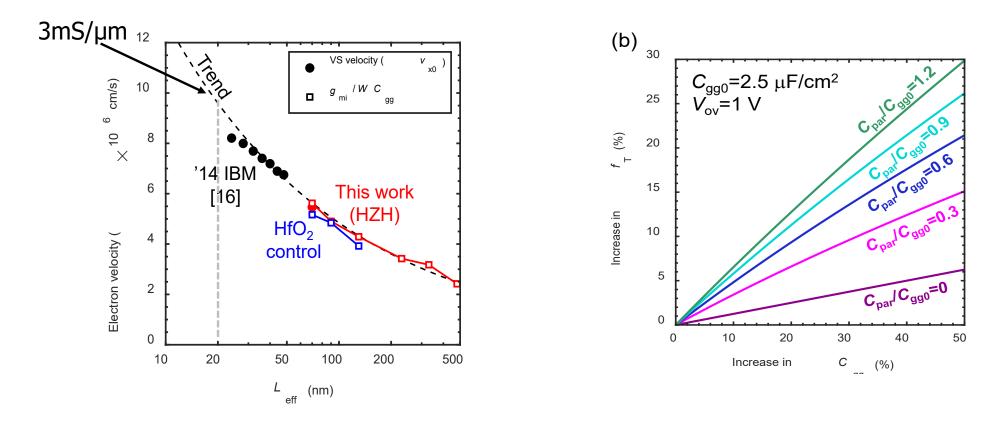

**DARPA** Trends In Velocity

No change in velocity, the increase in gm comes from increased Cox

Assumes the same Rs, Rd and Rg as 22 nm FDX and <u>air-gap spacer</u>

- Negative Capacitance allows to overcome the traditional barrier of losing mobility while trying to access EOT below 8A

- 6.5 A EOT without any degradation on velocity has been demonstrated

- Fabricated devices at Lg=90 nm shows record transconductance

- Further reduction to EOT=6A and an air-gap spacer (already in production research for digital MOSFETs) shows promise for planar FDSOI to reach 1 THz cut-off frequency

www.darpa.mil

2021 DARPA ERI Summit and MTO Symposium, online event, October 19-21, WORKSHOP: Next Generation Mixed-Mode Microelectronics, Wednesday, October 20, 3:15pm – 5:30pm presentation 5:00-5:15PM EDT https://eri-summit.darpa.mil/

### Looking to the Future Through a High-Speed InP Lens

Mark Rodwell University of California, Santa Barbara

The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

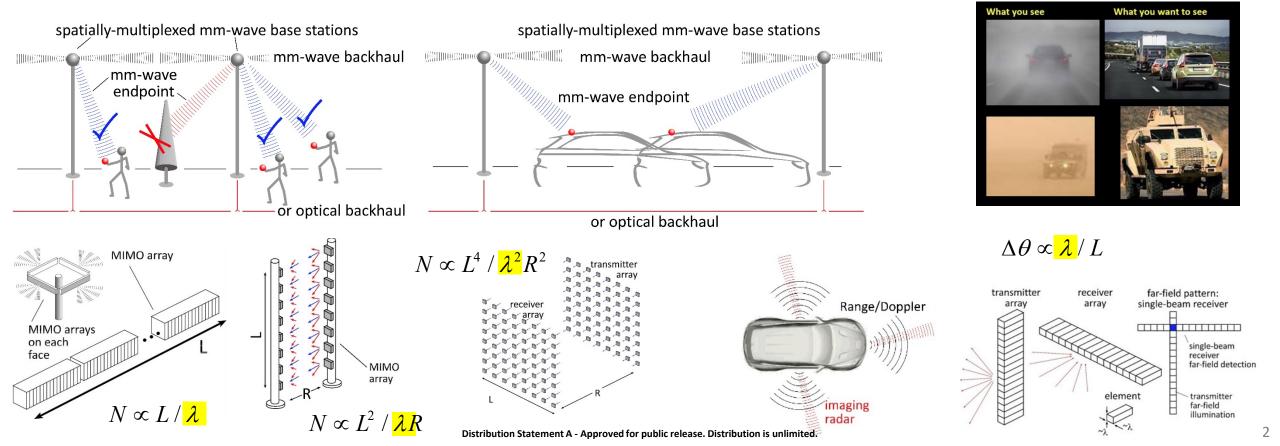

### 50-300GHz Wireless: Terabit Aggregate Capacities

Wireless networks: rapidly increasing demand. High frequencies → plentiful spectrum → high capacity Short wavelengths → many beams → massive capacity

#### 50-300GHz carriers, massive spatial multiplexing → Terabit hubs and backhaul links, near-video-resolution short-range radar

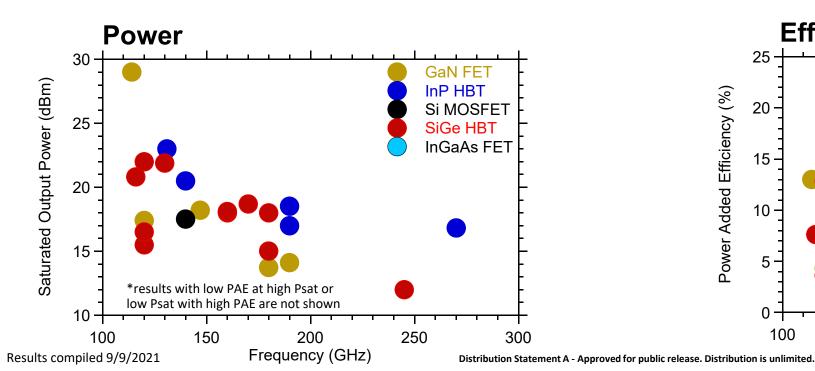

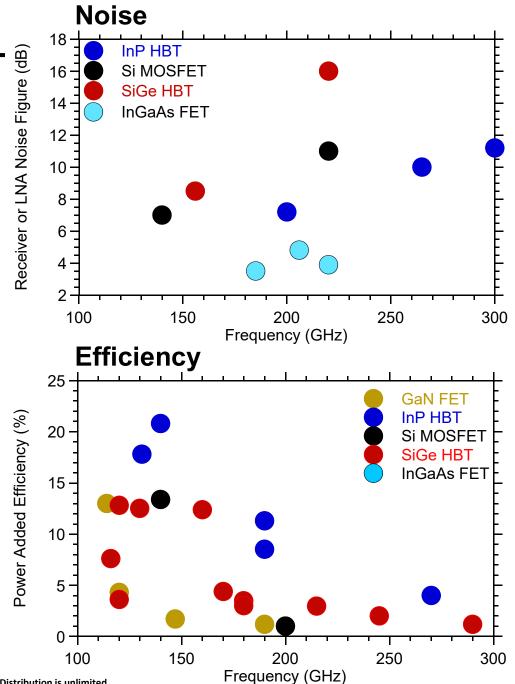

# CMOS alone won't do it.

Wireless needs: low noise, high power & efficiency.

**CMOS**: good to ~150GHz. Not much beyond.

InP HBT: record-efficiency 100-300GHz PAs

SiGe HBT: power better than CMOS, lower PAE than InP HBT

GaN HEMT: record power below 100GHz. Bandwidth improving

InGaAs-channel HEMT: world's best low-noise amplifiers

# Why InP Bipolar Transistors ?

#### InP: excellent high-field transport

high (peak) electron velocity:  $3.5 \times 10^7$  cm/s (Si:  $1.0 \times 10^7$  cm/s) wide bandgap  $\rightarrow$  high breakdown field

### InGaAs base, base-emitter heterojunction:

very low base sheet resistance

#### **Implications:**

Higher ( $f_{\tau}$ ,  $f_{max}$ ) at a given scaling node Higher operating voltage\* at a given ( $f_{\tau}$ ,  $f_{max}$ )

\*Transistor voltage limits are too complex to summarize with BVCEO. BVCBO vs. BVCEO vs. safe operating area ? Bottom line: look at ( $V_{ce,max}$ ,  $J_{e,max}$ ) used in published IC data for a given IC technology.

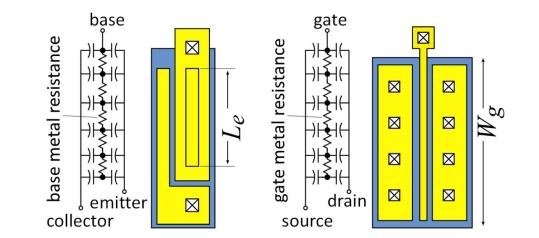

# **Bipolar Transistor Scaling Laws**

Narrow junctions.

**Thin layers**

**High current density**

**Ultra low resistivity contacts**

| to double the bandwidth:             | change         |  |

|--------------------------------------|----------------|--|

| emitter & collector junction widths  | decrease 4:1   |  |

| current density (mA/μm²)             | increase 4:1   |  |

| current density (mA/μm)              | constant       |  |

| collector depletion thickness        | decrease 2:1   |  |

| base thickness                       | decrease 1.4:1 |  |

| emitter & base contact resistivities | decrease 4:1   |  |

# InP Bipolar Scaling Roadmap

Narrow junctions.

Thin layers

**High current density**

Ultra low resistivity contacts

| emitter             |                            |                             |                             |                   |

|---------------------|----------------------------|-----------------------------|-----------------------------|-------------------|

| junction width      | 256                        | 128 🗸                       | 64 <mark>(?)</mark>         | nm                |

| access resistivity  | 8                          | 4                           | 2                           | Ω–μm <sup>2</sup> |

| base                |                            |                             |                             |                   |

| thickness           | 2.5                        | 2.5                         | 2.0                         | nm                |

| contact width       | 256                        | 128                         | 64                          | nm                |

| contact resistivity | 10                         | 5                           | 2.5                         | Ω–μm <sup>2</sup> |

| collector           |                            |                             |                             |                   |

| thickness           | 150                        | 100                         | 70                          | nm                |

| current density     | 2.8                        | 3.5                         | 3.5                         | mA/µm             |

| breakdown (ceo)     | 4.6 <sub>meas</sub>        | 3.5 <sub>meas</sub>         | 3.1 <sub>meas</sub>         | V                 |

| f <sub>t</sub>      | <b>416</b> <sub>meas</sub> | 520 <sub>meas</sub>         | 900 <sub>calc.</sub>        | GHz               |

| f <sub>max</sub>    | 755 <sub>meas</sub>        | <b>1150</b> <sub>meas</sub> | <b>1600</b> <sub>calc</sub> | GHz               |

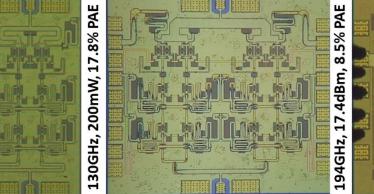

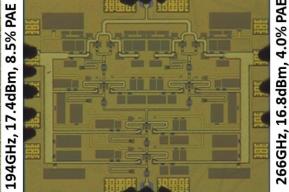

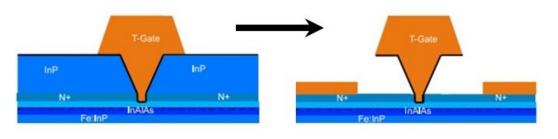

### 250nm / 700GHz InP HBT Technology

PAE

8%

Ñ

5dBI

Ñ

140GHz

Teledyne 250nm InP HBT Technology

#### 204.9GHz static divider (M/S latch) Giffith et al, 2010 CSICS

#### 200GHz power amplifier: 23dBm

190GHz transmitter: 16.5dBm power M. Seo et al, 2021 IMS

**200GHz receiver:** 8.0dB noise figure M. Seo et al, 2021 IMS

#### 130-270GHz power amplifiers: record efficiencies

Ahmed et al, 2020 IMS, 2020 EuMIC, 2021 IMS, 2021 RFIC

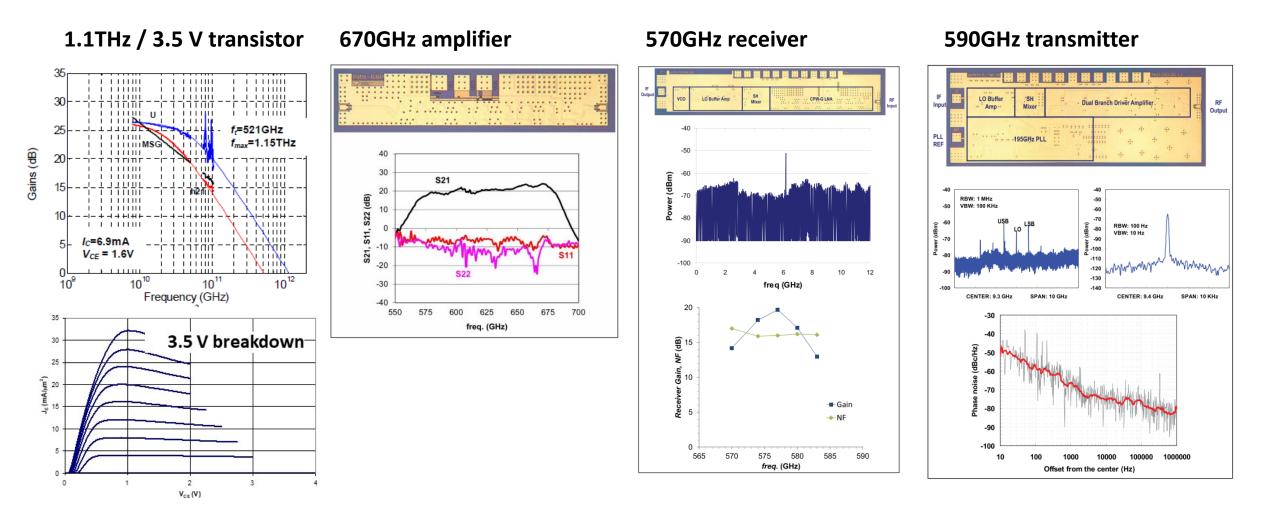

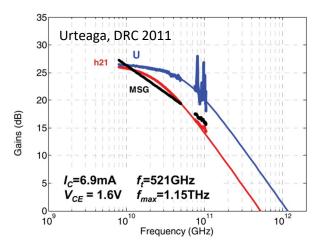

### 130nm / 1.1THz InP HBT Technology

Teledyne: M. Urteaga et al: 2017 IEEE Proceedings

#### 529GHz dynamic divider

Seo et al, 2015 IEICE Electronics Express

Divider OUT 10-stage drive amplifier Balun

**688GHz fundamental oscillator** Urteaga et al, 2017 IEEE Proceedings

Distribution Statement A - Approved for public release. Distribution is unlimited.

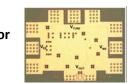

# Towards a 2THz HBT: The key challenges

Baraskar et al, Journal of Applied Physics, 2013

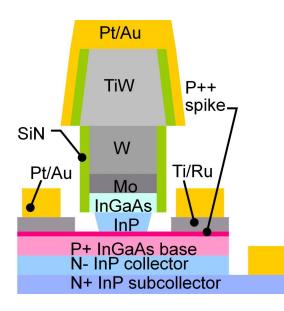

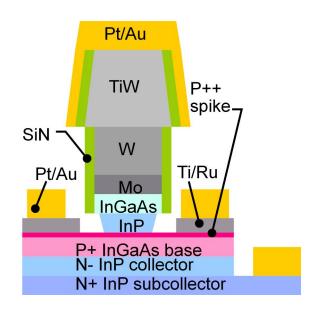

+ InP subcollecto

# Towards a 2 THz SiGe Bipolar Transistor

#### **Similar scaling**

InP: 3:1 higher collector velocity SiGe: good contacts, buried oxides

#### Key distinction: Breakdown

InP has:

thicker collector at same  $f_{\tau}\text{,}$  wider collector bandgap

#### **Key requirements:**

low resistivity Ohmic contacts note the high current densities

Assumes collector junction 3:1 wider than emitter. Assumes SiGe contacts no wider than junctions: pessimistic

|                     | InP  | SiGe |                                 |

|---------------------|------|------|---------------------------------|

| emitter             |      |      |                                 |

| junction width      | 64   | 18   | nm                              |

| access resistivity  | 2    | 0.6  | $\Omega$ – $\mu$ m <sup>2</sup> |

| base                |      |      |                                 |

| contact width       | 64   | 18   | nm                              |

| contact resistivity | 2.5  | 0.7  | $\Omega$ – $\mu$ m <sup>2</sup> |

| collector           |      |      |                                 |

| thickness           | 53   | 15   | nm                              |

| current density     | 36   | 125  | mA/µm²                          |

| breakdown           | 2.75 | 1.3? | V                               |

| f <sub>τ</sub>      | ~1.0 | ~1.0 | THz                             |

| f <sub>max</sub>    | ~2.0 | ~2.0 | THz                             |

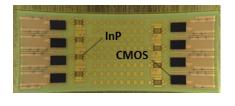

### InP HBTs: applications

#### Complex ICs X

ADCs, DACs, fast serial links ... Many transistors, tight CMOS integration Small high-value instrument market: front-ends for 100GS/s ADCs...

### 50-300GHz wireless front-ends 🗸

Application: record-efficiency PAs (30-300mW) Application: low-power, high-performance RF front-ends. Low-Just like GaAs HBT in today's 4G cell phones

# InP HBTs: research and development

### InP/CMOS monolithic integration X

Instead, put close together in same RF package

### Manufacturability and cost

High yield for ~100-transistor RF front-end ICs.

### Improved 50-300GHz PA efficiency 🗸

More  $f_{max}$  at the same  $f_{\tau}$ , and  $V_{br}$ : more gain  $\rightarrow$  higher PAE, class B, Doherty, etc. Scaling to 128nm and 64nm nodes but with 256nm node collector thickness.

### Integration density 🗸

Denser interconnects: denser ICs for 200+GHz arrays, for PA efficiency

### 300-2000GHz wireless X

High atmospheric loss: just a few applications (space, short-range concealed weapons imaging radar)

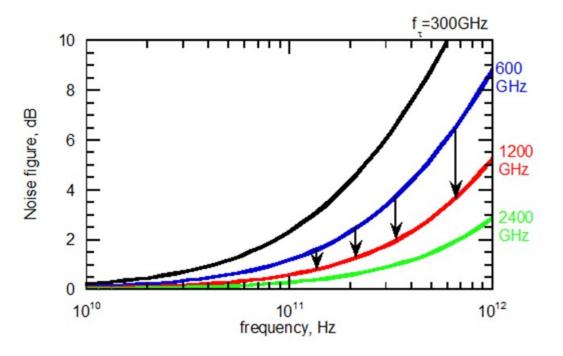

# FETs (HEMTs): key for low noise

#### Increased $f_{\tau}$ : less receiver noise

3dB less receiver noise: 2:1 less transmit power smaller PAs, less DC power

#### State of the art:

1.5 THz transistor f<sub>max</sub>

1.0 THz amplifiers

Xiaobing Mei, et al, IEEE EDL, April 2015 (Northrop-Grumman)

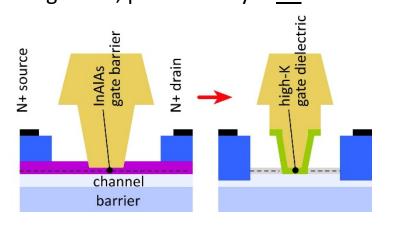

### InP MOS-HEMTs: faster, more manufacturable ?

#### Scaling limit: gate insulator thickness

HEMT: InAlAs barrier: tunneling, thermionic leakage solution: replace InAlAs with thin ZrO<sub>2</sub> dielectric

Scaling limit: source access resistance HEMT: InAlAs barrier is under N+ source/drain solution: regrowth, place N+ layer on InAs channel

Sacrificial-layer gate process for manufacturability Standard 20nm E-beam T-gate: limits IC yield MOS-HEMT: can use sacrificial-layer process instead

Markman et al, 2021 DRC

# For Q&A discussion

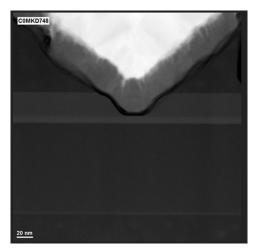

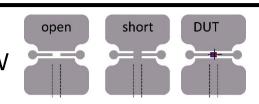

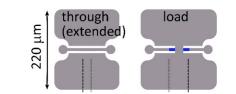

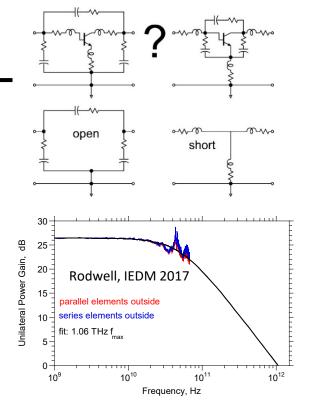

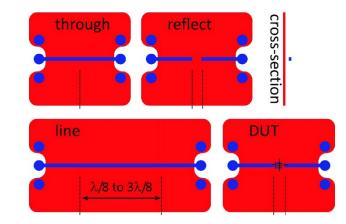

# **THz Transistor Measurements**

#### Simple pads:

Substrate coupling: need small pads, narrow CPW Ambiguity in pad stripping order. UCSB 130nm HBTs: order not important. Add through & load to remove ambiguity

#### **On-wafer through-reflect-line:**

No ambiguity from pad stripping. Calibration to line Zo Still must avoid substrate mode coupling CPW particularly vulnerable. better: thin-film microstrip or ~25 μm substrate with TSV's

D. F. Williams, A. Young, M. Urteaga, "A Prescription for Sub-Millimeter-Wave Transistor Characterization," IEEE Transactions on Terahertz Science and Technology, July 2013 Distribution Statement A - Approved for public release. Distribution is unlimited.

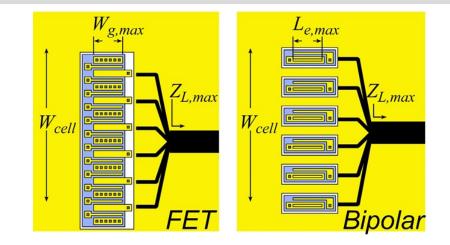

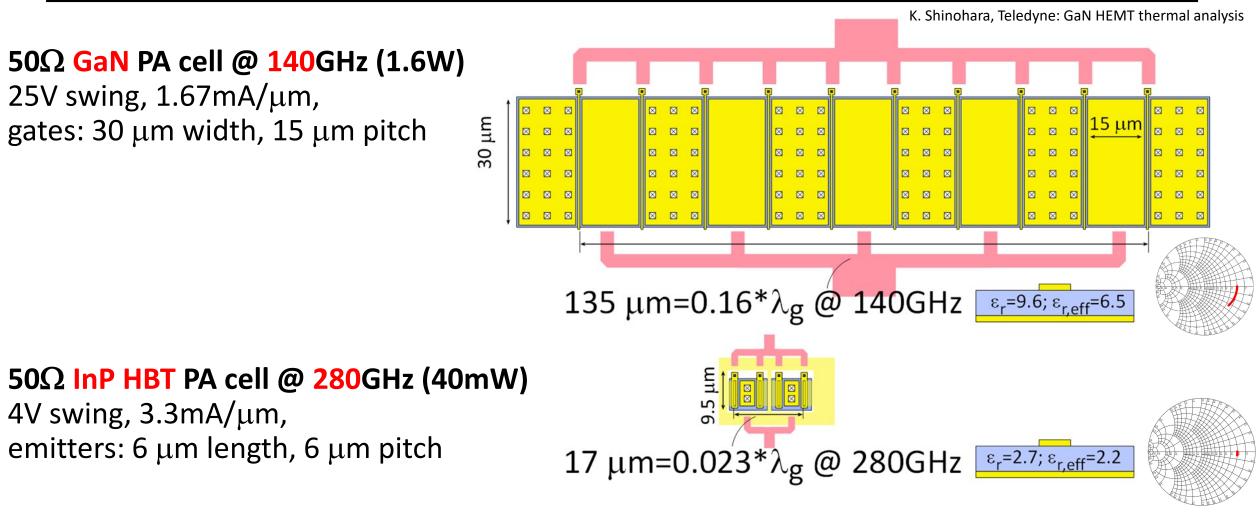

### Current density, finger pitch limit cell output power

Electrode *RC* charging time  $\propto$  (finger length)<sup>2</sup> Maximum finger length  $\propto 1/\sqrt{\text{frequency}}$ Current per finger  $\propto 1/\sqrt{\text{frequency}}$

Maximum cell width  $\propto 1/$  frequency Maximum number fingers  $\propto 1/$  frequency Maximum current per cell  $\propto 1/$  frequency<sup>3/2</sup>

Maximum RF power per cell  $\propto$  (maximum load resistance) (maximum current)<sup>2</sup>  $\propto 1/(\text{frequency})^3$

Compare to Johnson F.O.M.: maximum power per cell  $\propto$  (maximum voltage)<sup>2</sup>/(minimum load resistance)  $\propto 1/(\text{frequency})^2$

### Current density, finger pitch limit cell output power

High  $V_{br}$ , low  $I_{max}$ ? Device sized to drive 50 $\Omega$  might approach  $\lambda_g/4$  width. Small finger pitch is critical; limited by thermal design