Challenges and Solutions to Thermal Management in 3D Microsystems

Muhannad Bakir

Georgia Institute of Technology

mbakir@ece.gatech.edu

Distribution Statement A – Approved for public release. Distribution unlimited.

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA).

The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

## Thermal Challenges in 3DHI

$\rightarrow$ Limited cooling

### Key thermal challenges are:

- Inability to extract heat from 3DHI, limiting power, performance, and functionality

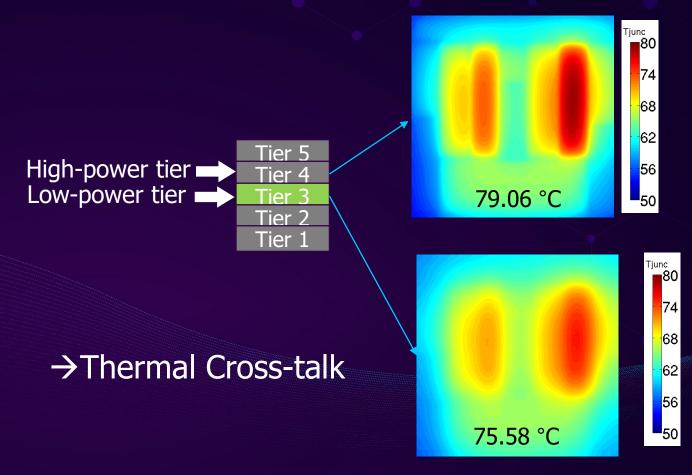

- Thermal cross-talk in 3DHI, impacting lower-power and temperature sensitive devices

- Typical form factor for cooling is large

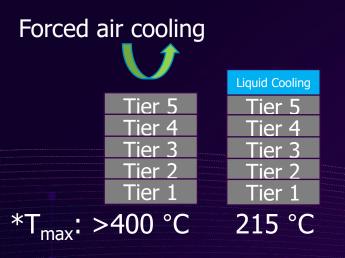

\*Assuming 300 W/cm<sup>2</sup> per tier

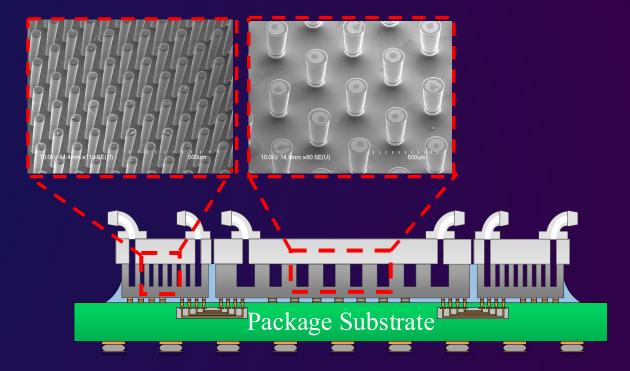

## Within 3D Stack Microfluidic Cooling

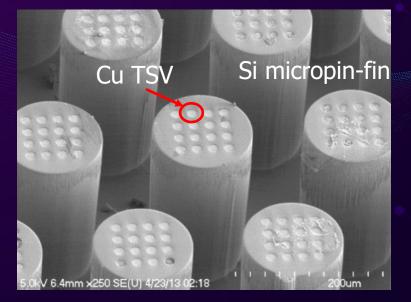

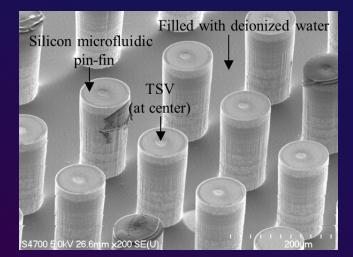

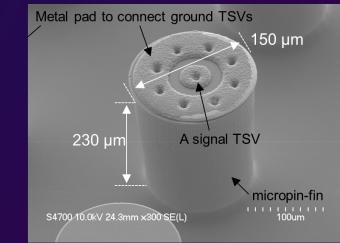

Silicon micropin-fin heat sink with integrated TSV

#### Tier 5 Liquid Cooling Forced air cooling Tier 4 Liquid Cooling Liquid Cooling Tier 3 Tier 5 Tier 5 Liquid Cooling Tier 4 Tier 4 Tier 2 Tier 3 Lier 3 Tier Liquid Cooling īer Tier Tier Tier \*T<sub>max</sub>: >500 °C 215 °C 48 °C

Electrical

performance

Thermal performance

Manufacturability, Integration, Reliability

Distribution Statement A – Approved for public release. Distribution unlimited

## Microfluidic Cooling Integration and Benchmarking

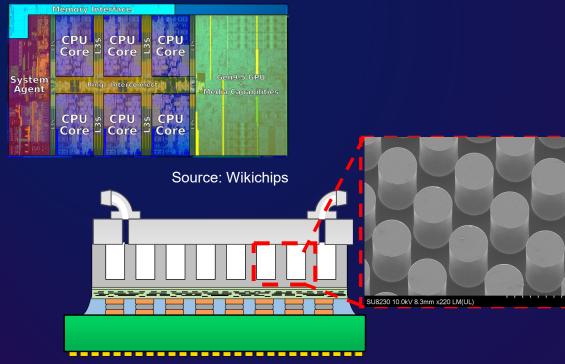

Etched micropin-fins on Intel i7-8700K Die

- Significantly smaller form factor (microscale)

- Relative to cold-plate, estimated ~40% lower thermal resistance

#### Intel Stratix 10 2.5D FPGA (4 transceivers)

- Optimized microscale heat sink for power density

- >10x reduction in thermal-crosstalk relative to air-cooled heat sink

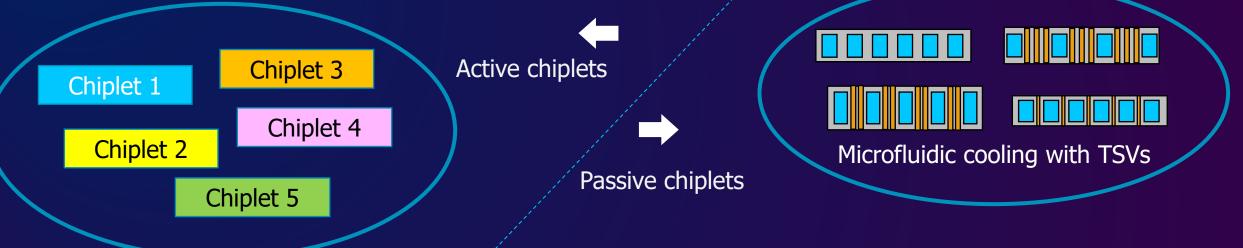

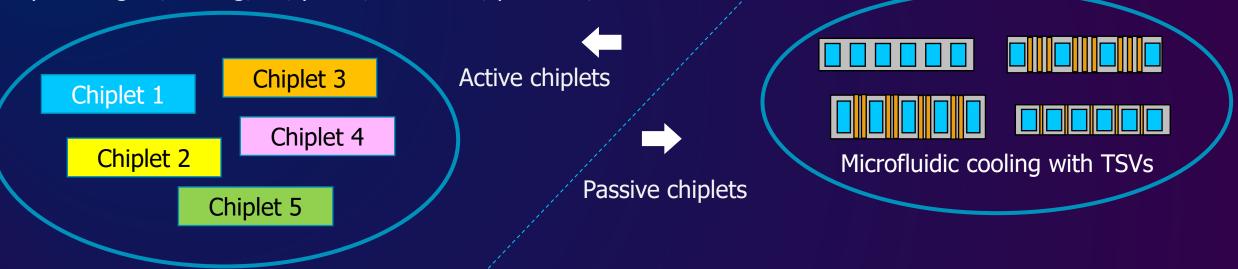

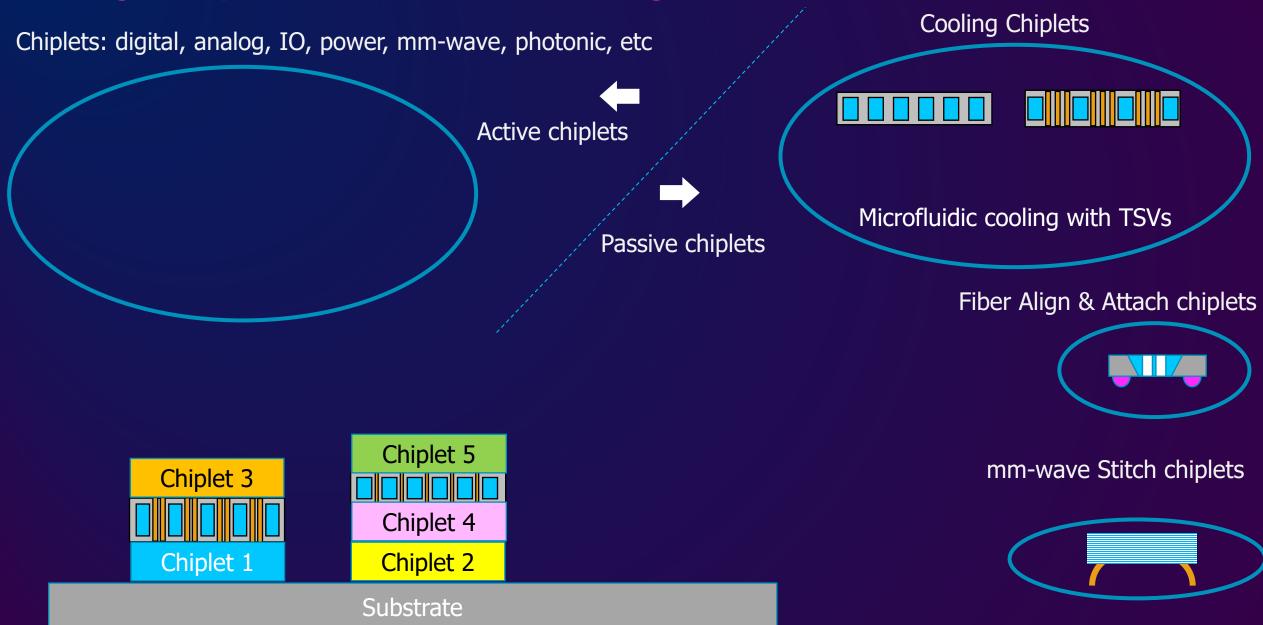

## Using Chiplets to Build 'Package Functions'

Chiplets: digital, analog, IO, power, mm-wave, photonic, etc

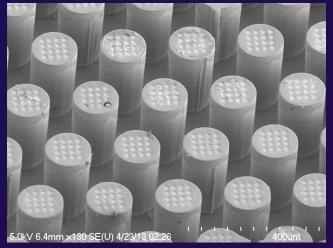

#### Single TSV in dense heat sink

#### TSV bundle in coarse heat sink

Distribution Statement A – Approved for public release. Distribution unlimited

#### Coax TSV in microfluidic heat sink

**Cooling Chiplets**

## Using Chiplets to Build 'Package Functions'

Chiplets: digital, analog, IO, power, mm-wave, photonic, etc

**Cooling Chiplets**

## Using Chiplets to Build 'Package Functions'

Distribution Statement A – Approved for public release. Distribution unlimited.

# THANK YOU