# New Applications Enabled by Complex 3D Microsystems

Josh Fryman, PhD Office of the CTO, Intel Fellow Aug 22, 2023

The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

ELECTRONICS RESURGENCE INITIATIVE 2.0

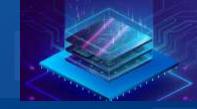

### Let's talk about memory for a moment ...

#### The real world is 3D (or higher)

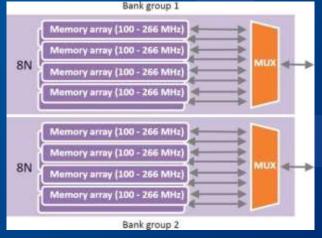

#### Memory is 2D internally

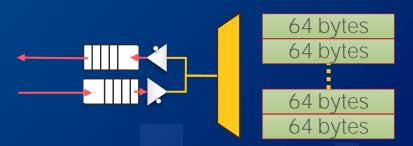

#### Which we make look 1D

Image Credit: https://www.cgtrader.com/3d-models/architectural/architectural-str

**DARPA ERI 2.0 Summit**

Image Credit: Intel Corporation Image Credit:

https://www.semiconductor-digest.com/the-history-and-future-of-dram-architecture-in-different-application-domain

© Intel Corporation

https://www.cgtrader.com/3d-models/architectural/architectural-street/bilding-complex

DARPA ERI 2.0 Summit

© Intel Corporation

Intel Corporation

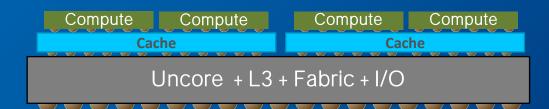

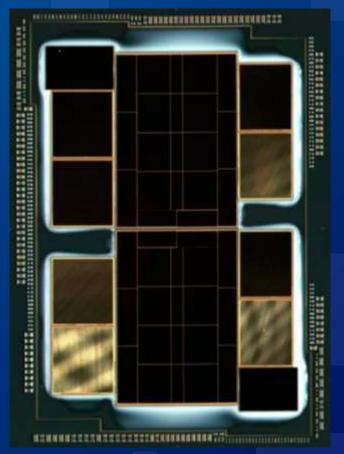

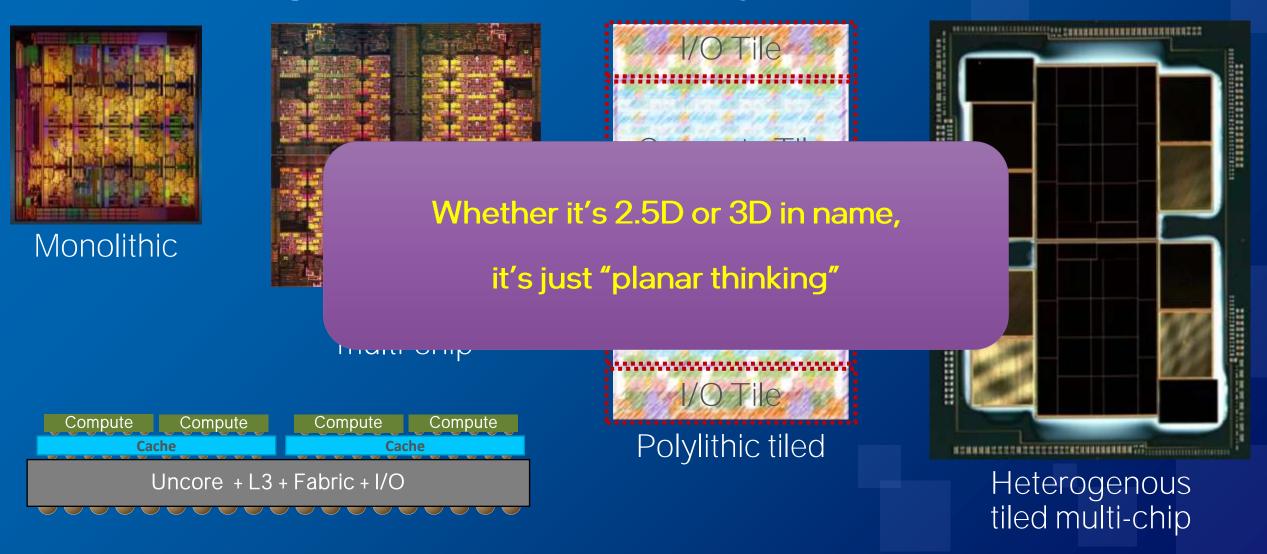

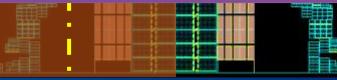

### Chip design: are we 3D today?

Monolithic

#### Polylithic multi-chip

## Heterogenous tiled multi-chip

#### DARPA ERI 2.0 Summit

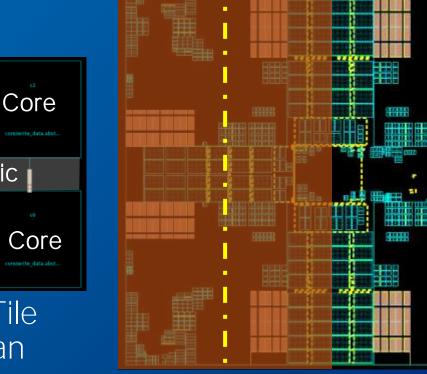

### Chip design: are we 3D today?

### What about cutting-edge 3D?

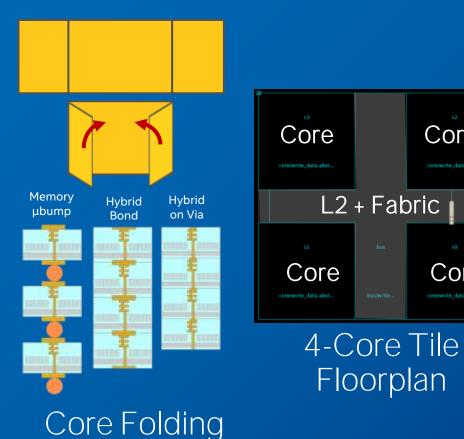

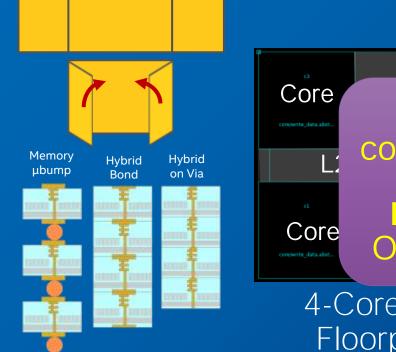

#### Fold Line Concept with Hybrid Bonding

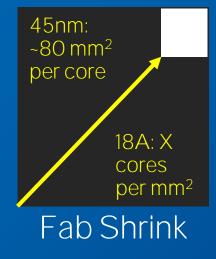

"Shrink"

### What about cutting-edge 3D?

Trade-offs in performance and area vs. complexity of design, thermals, and validation

It's a fancy "planar" thinking – with a twist: O(1M) hybrid bonding connections per mm<sup>2</sup>

4-Core Tile Floorplan

Fold Line Concept with Hybrid Bonding

"Shrink"

Core Folding

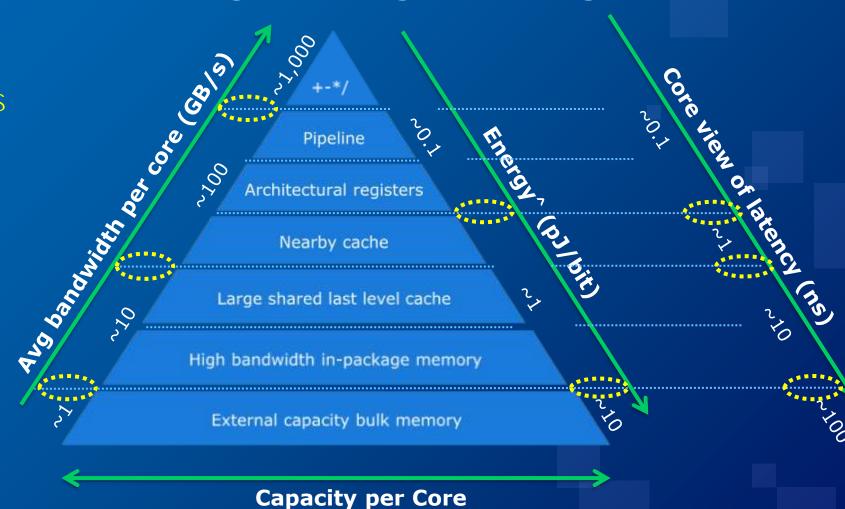

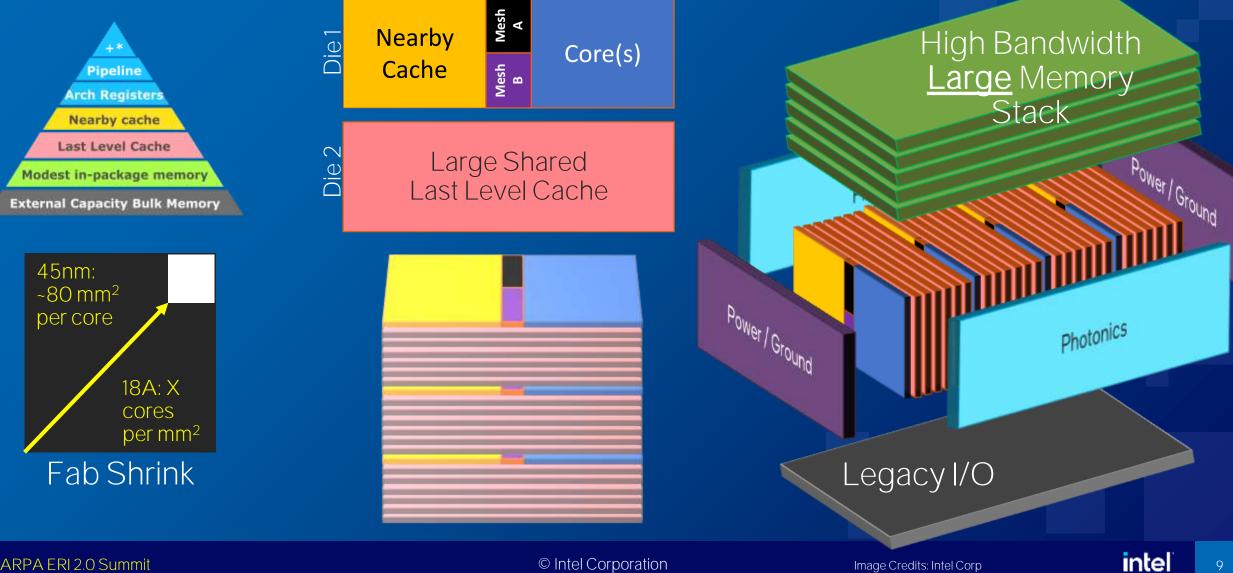

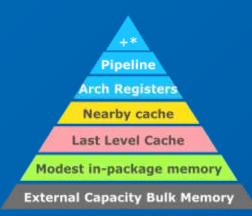

### But are we exploiting the right things?

Tapering divisions in bandwidth, energy, and latency are opportunities to optimize

<sup>^</sup>Not counting overheads for access

© Intel Corporation

### 3D as a spatial concept, not planar

DARPA ERI 2.0 Summit

© Intel Corporation

### 3D as a spatial concept, not planar

Nearby <sup>5ສຼ</sup>ັ Cache ຊູ

Die 1

Core(s)

High Bandwidth Large Memory Stack

Photonics

Match trade-offs to natural architecture inflection points – speeds and feeds.

Use all 6 faces of "cubic 3D" and simplify: O(1k) hybrid bonding connections per mm<sup>2</sup>

Legacy I/O

intel

ower/Grou

### Application breakthroughs of dense 3DHI

#### Aurora 2.0 ExaFLOP System

- 1 Rack ≈ 9.8 m<sup>3</sup>

- 128 Xeons + 384 X<sup>e</sup> + Slingshot fabric

- Fits in 3D cube at 40 mm per side

- >100,000x smaller volume

#### Apple's VisionPro AR Headset

- Multiple types of silicon, packages

- Size, weight, and power are limiters

- Rice  $\approx 2 \text{ mm} \times 2.75 \text{ mm} \times 6 \text{ mm} \text{ per grain}$

- Fits Apple silicon <u>and</u> ~0.5 TB memory

[1] https://www.ncbi.nlm.nih.gov/pmc/articles/PMC6145214

© Intel Corporation

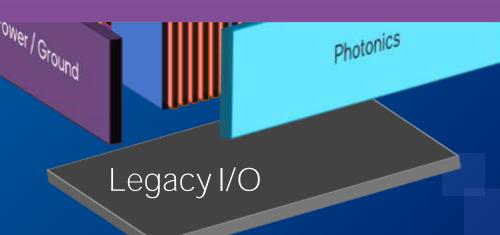

### Challenges to achieving dense 3D

er / Ground

#### Manufacturing:

- edge polish

- right-angle attach

- via density

- bonding speed

- rework support

- redundancy

- tooling Z-height

- wafer thinning

#### Power and Thermals:

- thermal density

- power delivery

- cooling layers

- heterogeneous material

Photonics

#### EDA:

- rotated die

- taper point isolation

- non-planar libraries

- formal verification

- DF<all>1,000 layers

- scan chain time

- tests and coverage

#### Design:

- graceful degradation

- extreme interop

- built-in redundancy

- pluggable modules

- abstractions for all

Legacy I/O

### Challenges to achieving dense 3D

#### Manufacturing:

- edge polish

- right-angle attach

- via density

- bonding speed

- rework support

- redundancy

- tooling Z-height

- wafer thinning

#### Power and Thermals:

- thermal density

- power delivery

- cooling layers

- heterogeneous material

#### High Bandwidth Large Memory

Modularity in design, reworkable components, interop standards, and time to develop these tools and flows are critical to enabling this 3D "solution in a cube" future

### EDA:

- rotated die

- taper point isolation

non-planar libraries formal verification DF<all>1,000 layers scan chain time tests and coverage

#### Design:

- graceful degradation

- extreme interop

- built-in redundancy

- pluggable modules

- abstractions for all

© Intel Corporation