#### **ERI Design: IDEA and POSH**

MAGESTIC: Machine-Learning for Automatic Generation of Electronic Systems Through Intelligent Collaboration

Cadence Design Systems, NVIDIA and Carnegie Mellon University

IDEA and POSH Integration Exercise

Detroit, MI

July 17 – July 19, 2019

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions, and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

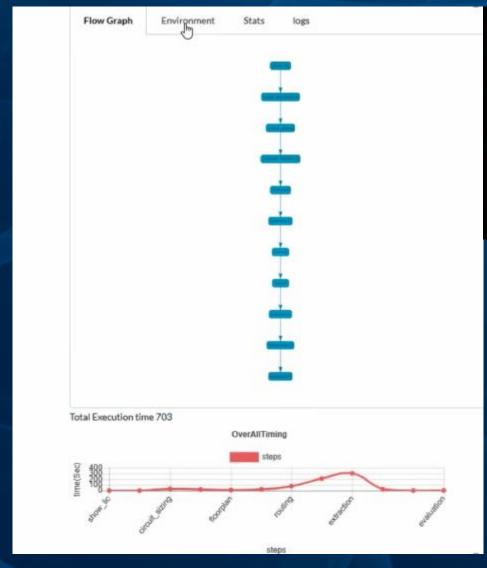

### MAGESTIC Program

- Team: Cadence Design Systems, NVIDIA and Carnegie Mellon University

- Goals:

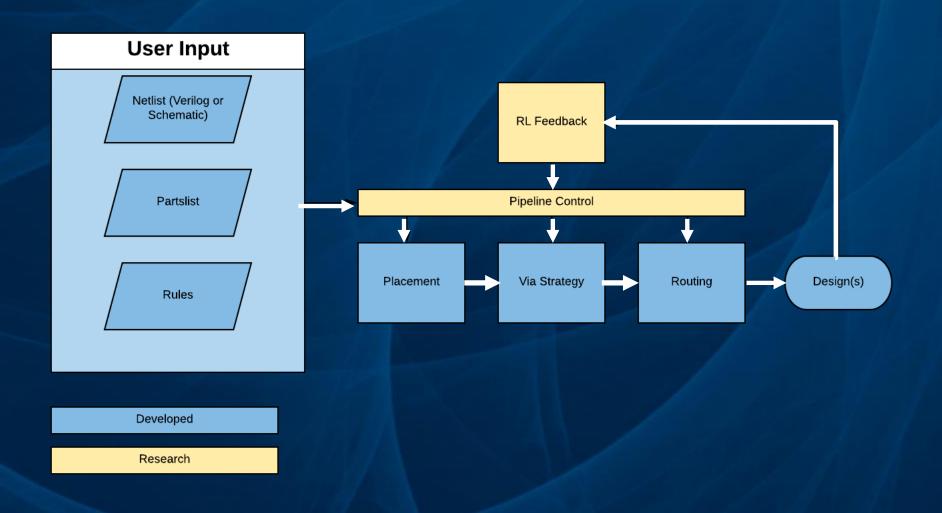

- No Human in the Loop (NHIL) Design Flow, Silicon Compiler in < 24 hours TAT</li>

- Research in Analog IC Design through Package and PCB Design

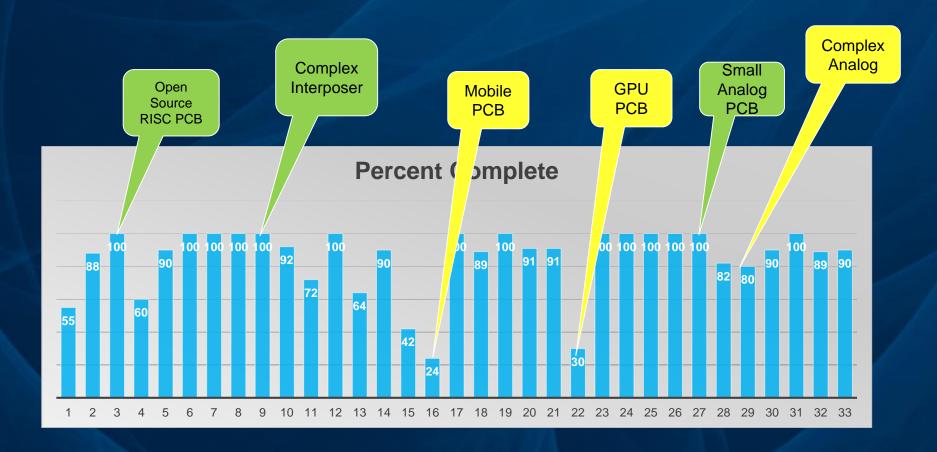

- Achieve Automated Design Across a Broad Spectrum of Designs in Year 2

- Agenda for Today:

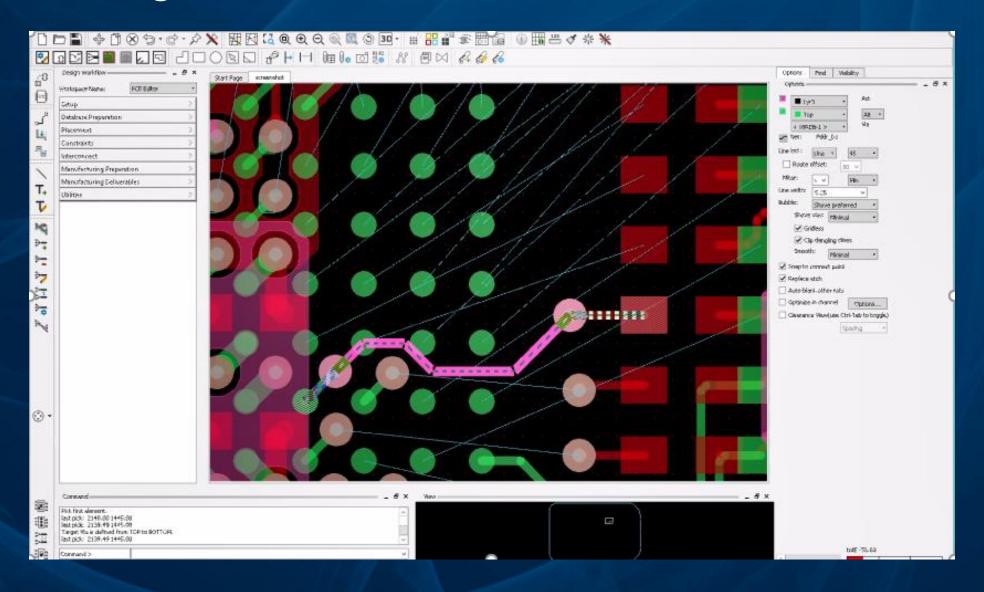

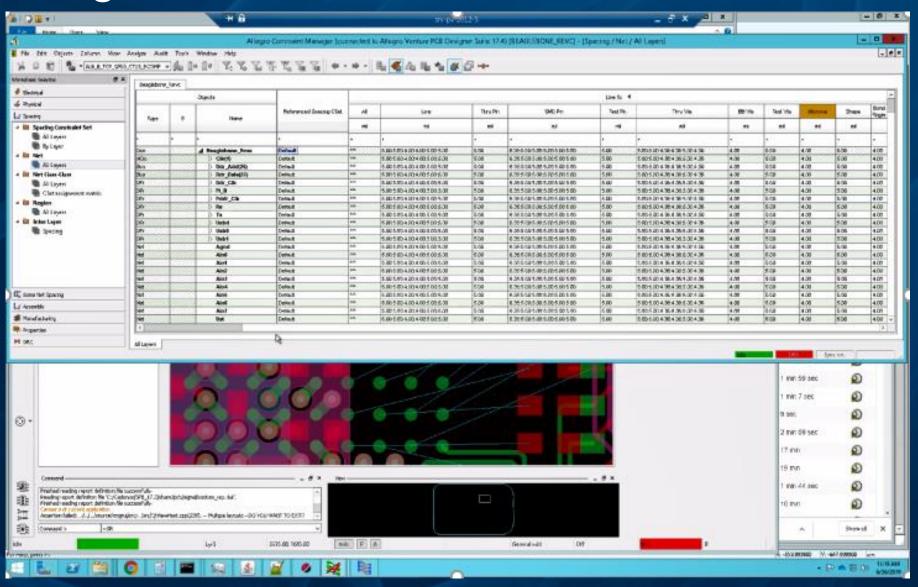

- Software Demonstration of NHIL Package and PCB Design Progress

- Focus for NHIL Package and PCB Design Research in Year 2

Taylor Hogan

- Software Demonstration of NHIL Analog IC Design Progress

- Focus for NHIL Analog IC Design Research in Year 2

Elias Fallon

Visit MAGESTIC Team to see Live Demos of the Design Data Presented Today

## PCB & Package Synthesis ERI Conference 2019

### **EDA Ages**

- The Dark AgeInteractive, NAIL

- The Industrial Age

NHIL for Some, Hope

- The Age of Enlightenment

NHIL for All, Explorations

### The Dark Ages

### The Dark Ages Continue

## The Industrial Age

### **Industrial Age**

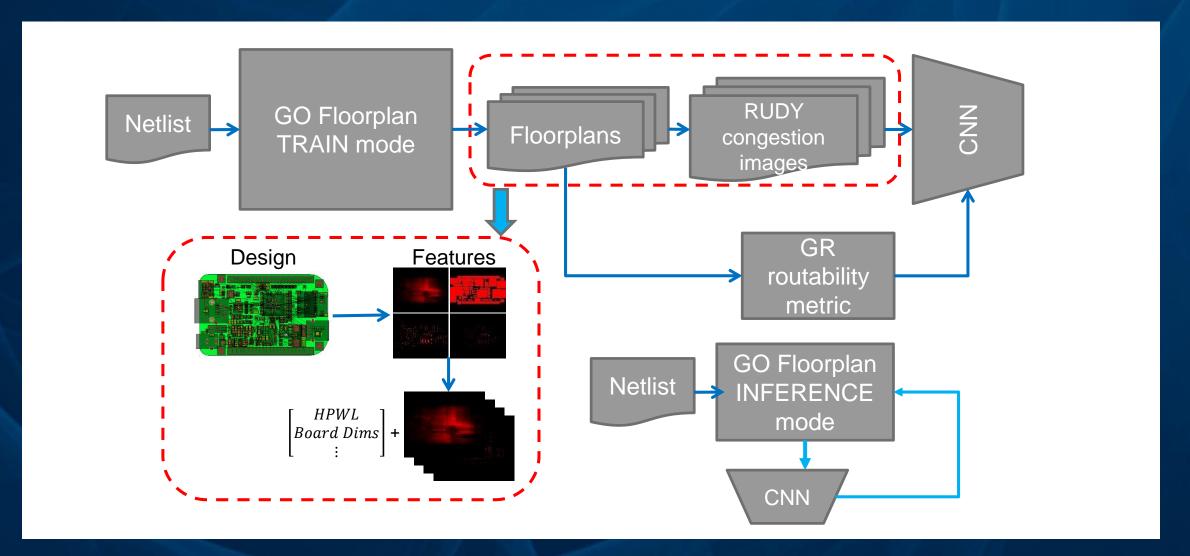

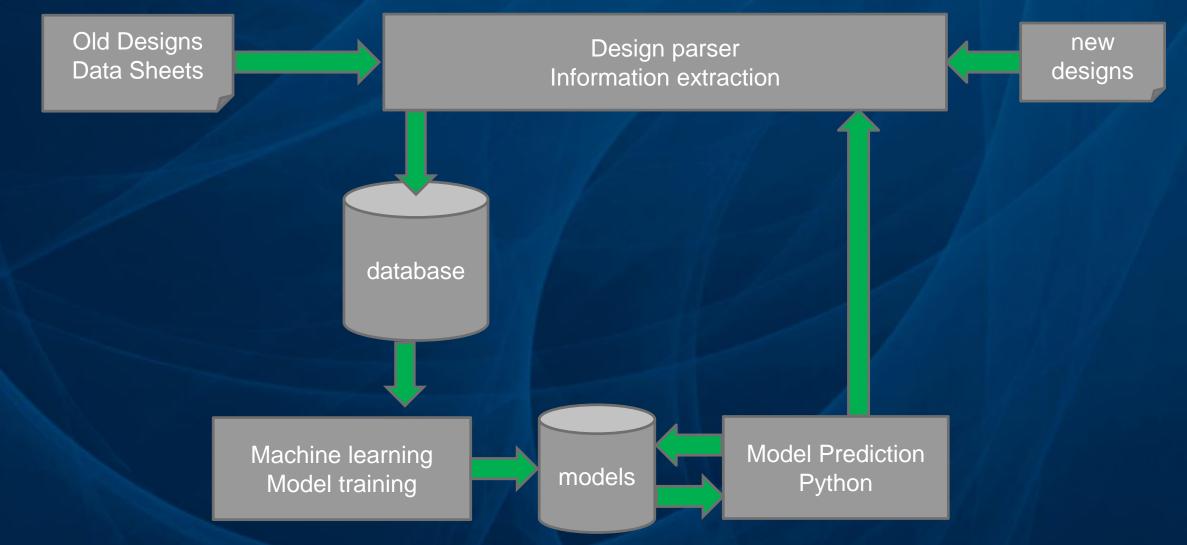

Training Neural Networks to Avoid Intractable Computational Problems

### The Industrial Age ... Hope

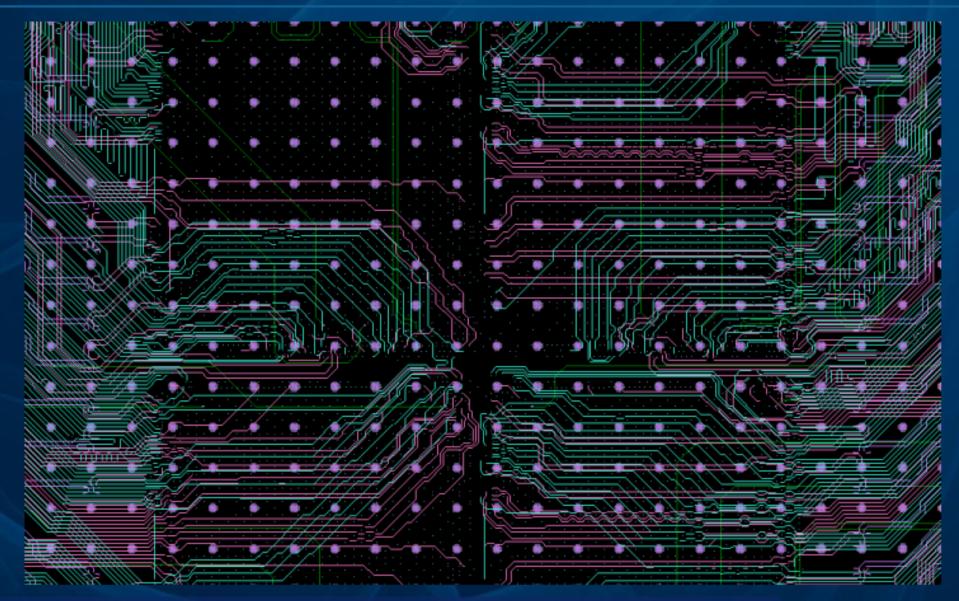

# Auto Router Comparisons- Test Case 1 Automatic routings of N-1 CPU interposer using the Manually routed and tuned N-1 CPU Interposer. Routing time: ~120 hours Al Global router. Routing time: ~ 30 minutes PCB West 2018, September 11-13, 2018, Santa Clara, CA

### Industrial Age Continues

# What Works What Does Not Work

### Achieving NHIL for All

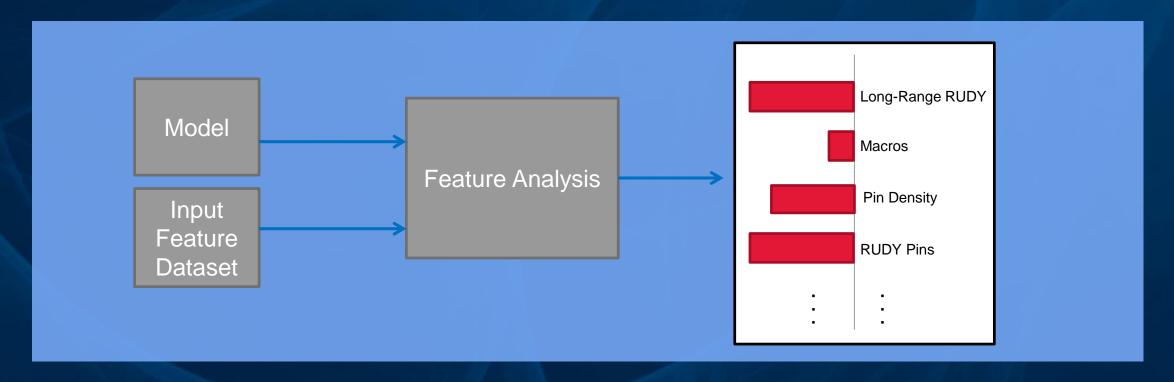

# Age of Enlightenment Feature Sensitivity Analysis

- Development of methods and tools that aid in the interpretability of neural networks by humans

- Explain what features matter

## Analog IC ERI Conference 2019

### **MAGESTIC Analog**

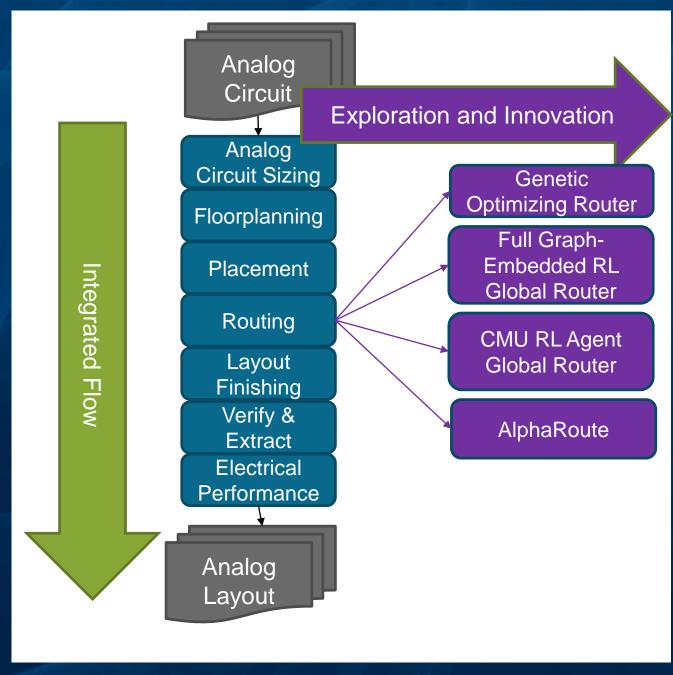

### Research Dimensions

- Integrated flow

- See complex interactions between steps

- Evaluate overall electrical performance

- Exploration and Innovation

- Creative research into new approaches

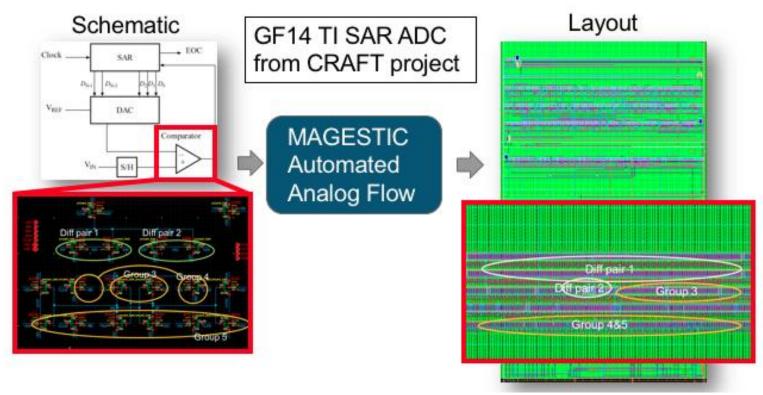

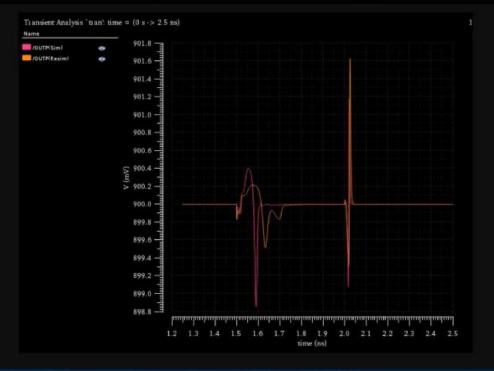

|                                                | Original CRAFT<br>GF14 sub-ADC +<br>Comparator<br>circuit<br>Schematic Only<br>Simulation | CRAFT GF14 sub-<br>ADC + Resized<br>Comparator for<br>yield<br>Schematic Only<br>Simulation | Original CRAFT GF14<br>sub-ADC (original<br>Comparator)<br>Post-Layout (CRAFT<br>taped-out) Simulation<br>with extracted parasitics | CRAFT GF14 sub-ADC<br>(original Comparator)<br>Post-Layout<br>(MAGESTIC-created)<br>Simulation with<br>extracted parasitics | CRAFT GF14 sub-ADC<br>(resized Comparator)<br>Post-Layout<br>(MAGESTIC-created)<br>Simulation with<br>extracted parasitics |

|------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Comparator Yield (Process<br>Corners/Mismatch) | 62%                                                                                       | 99%                                                                                         | 55%                                                                                                                                 | 51%                                                                                                                         | 100%                                                                                                                       |

| Comparator Yield (across<br>Vdd/Temp)          | 58%                                                                                       | 99%                                                                                         | 52%                                                                                                                                 | 47%                                                                                                                         | 100%                                                                                                                       |

| Effective Number of Bits (ENOB)                | 5.87                                                                                      | 6.64                                                                                        | 5.47                                                                                                                                | 5.70                                                                                                                        | 6.15                                                                                                                       |

ML based yield improvements

Within design metrics, better yield

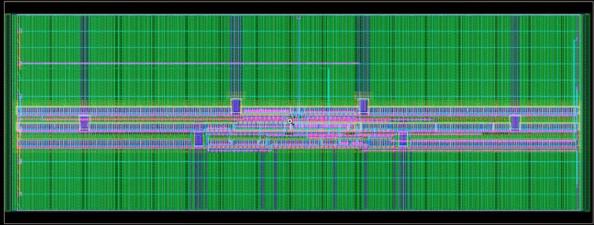

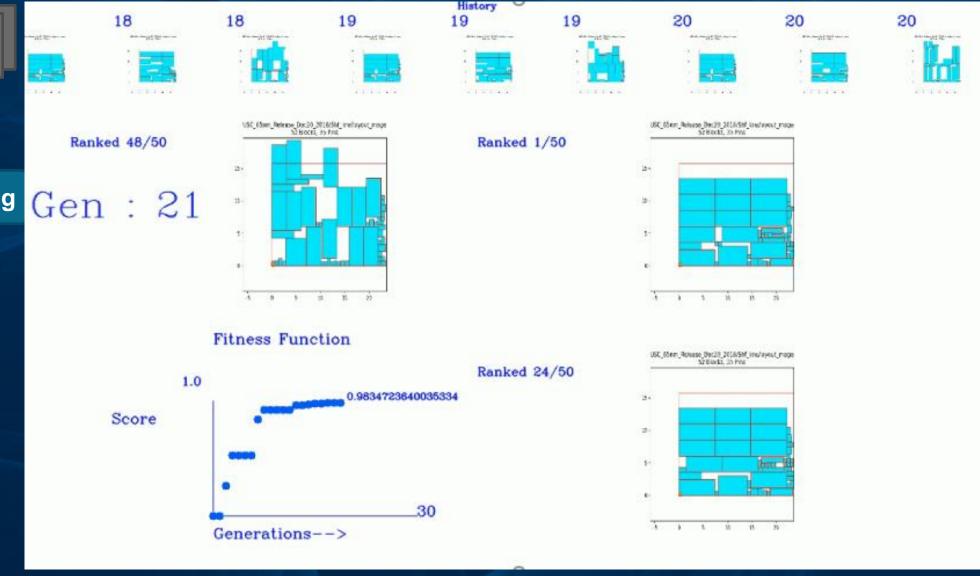

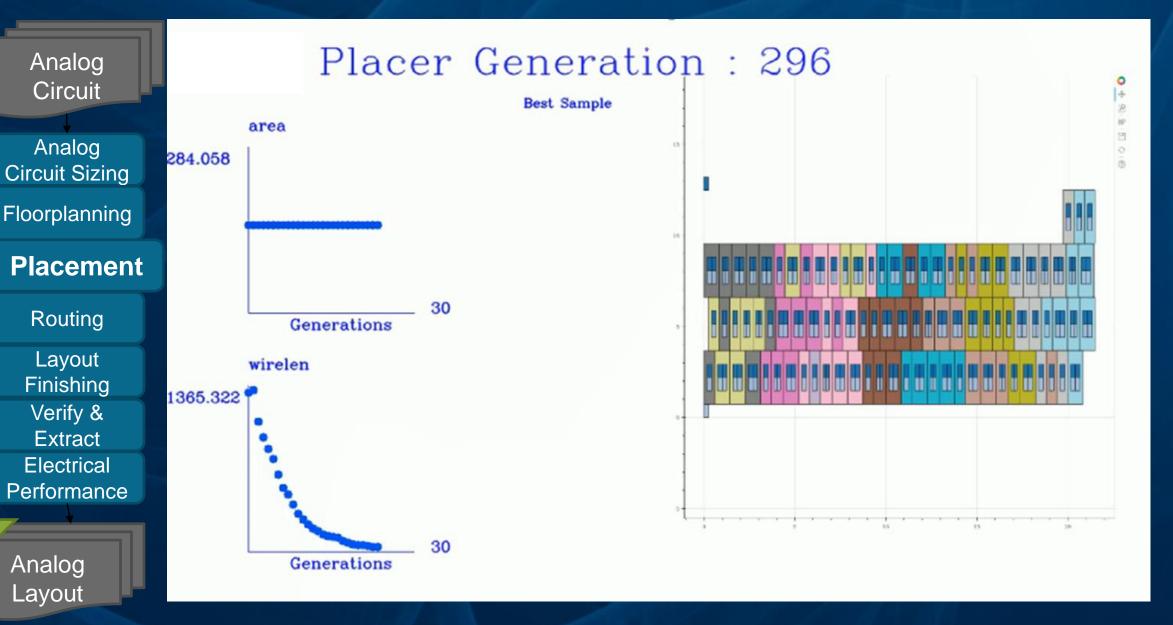

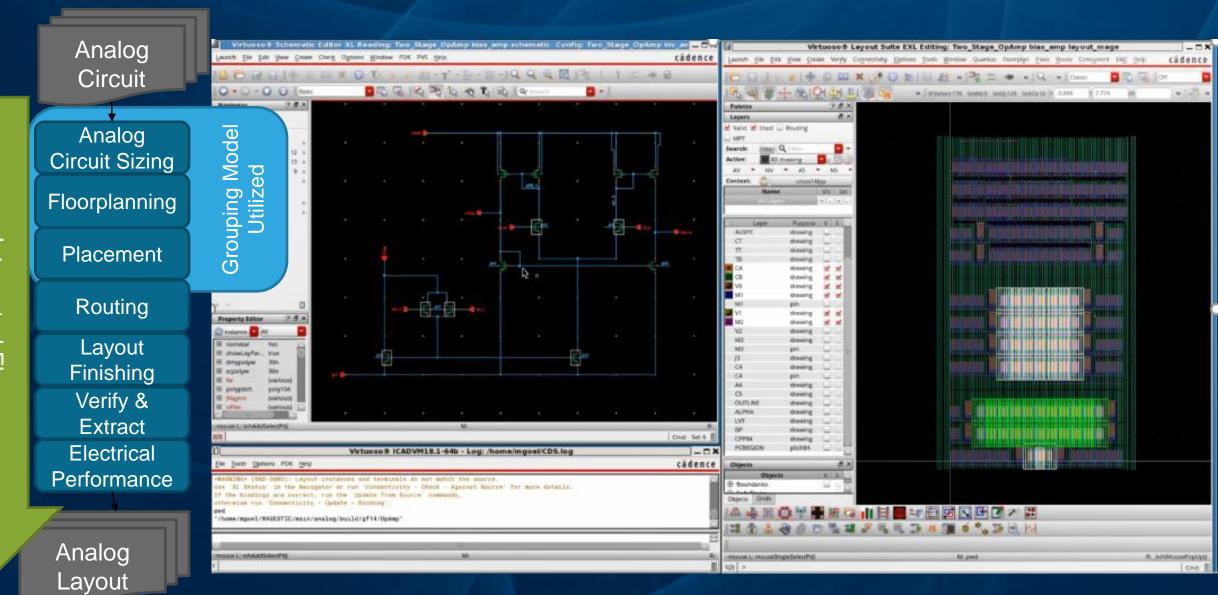

### Analog Circuit

Analog Circuit Sizing

Floorplanning

**Placement**

Routing

Layout

Finishing

Verify &

Extract

Electrical

Performance

Analog Layout

Analog

Layout

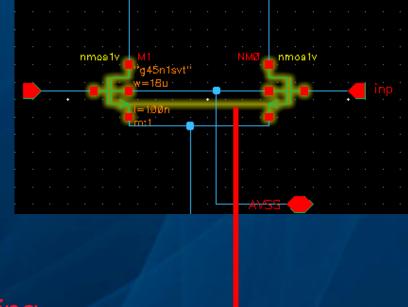

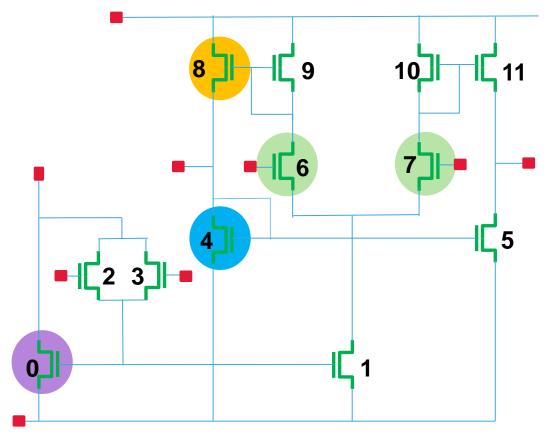

### Layout Group Prediction Problem

- It is common practice for layout designers to group devices that need good matching

- Grouped devices are placed closely together, and there may be interdigitation

- Grouping decisions are largely made from experience

- Even simulation cannot fully predict effects of grouping

- Can we learn them from good hand-crafted layouts?

- To formulate a machine learning problem, we need to define grouping as a label and predict it from schematic features

### **But Wait! There's More!**

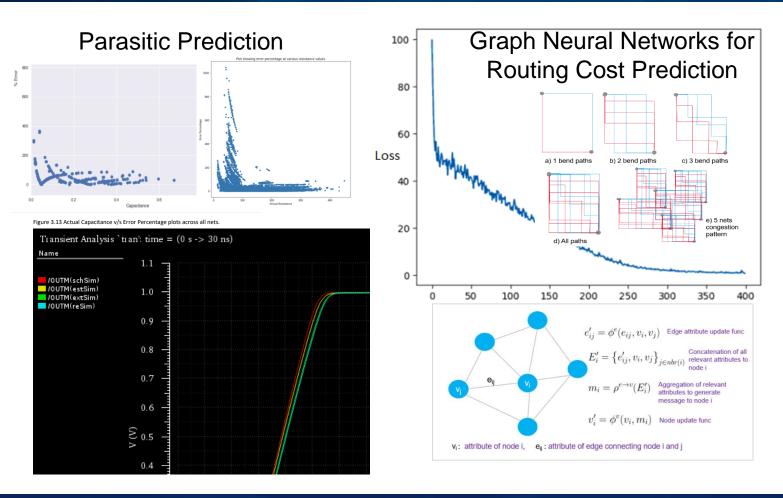

#### Exploration and Innovation

Please stop by during the IDEA Integration Exercise to see a demo or discuss in more detail many of our other exciting projects

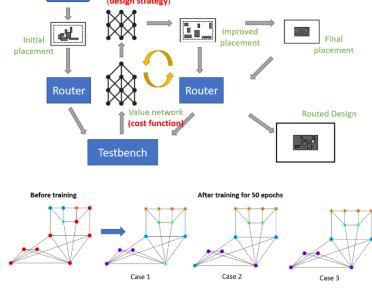

# AlphaRoute / AlphaAnalogDesign Updates Start (design strategy) | Policy network (des

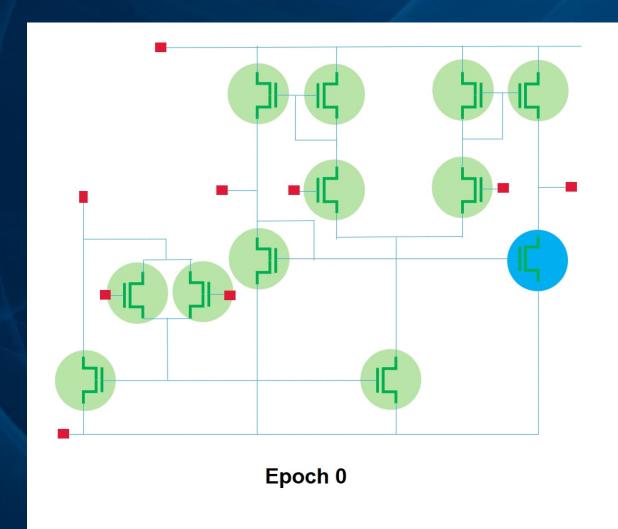

**Graph Convolutional Network (GCN)**

Representation of Circuit

Input

ReLU

ReLU

...

Relu

Relu

Suppose we are given the following (sparse) labels:

- Transistor 0, 4, 6, and 8 will be in *different* groups

- Transistor 6 & 7 belong to the same group

Can we train a reasonable grouping model using the netlist information?

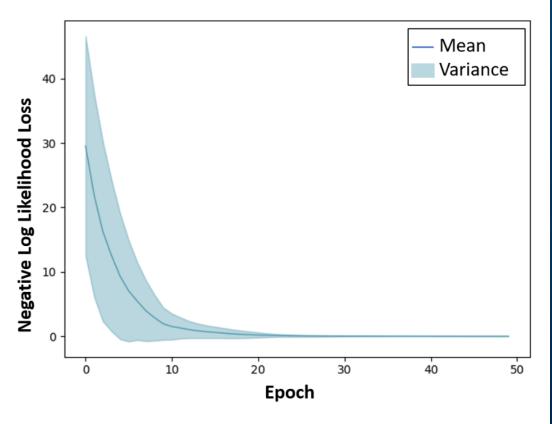

### **GCN Training for Grouping Cold Start Model**

The learning curve of 10 runs, each with a maximum of 50 epochs

#### Cadence Design Systems, NVIDIA and Carnegie Mellon University

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions, and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.