# IDEAL: An Intelligent Design Environment for Asynchronous Logic

PI: Rajit Manohar (Yale) Co-PIs: Keshav Pingali (UT Austin), Martin Burtscher (Texas State)

TEXAS **ATE** UNIVERSITY

The rising STAR of Texas

#### **Overview and goals**

- A parallel design flow for asynchronous logic

- Modularity

- permitting re-use (similar to software)

- "re-compile" only for technology-specific optimization

- Minimizes expectations from the implementation technology

- Built more like a software compiler than current EDA tools

- Operate on a core database

- "Passes" for optimization

- Share analysis phases at multiple levels of abstraction

- High-level design

- Circuit

- Physical

#### **Team and roles**

|         | Asynchronous<br>design & tools               | Parallel data-structures<br>& algorithms | GPU-based parallelization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|----------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Faculty | Fajit Manohar<br>(Yale)                      | Feshav Pingali<br>(UT Austin)            | Image: Constrained and the con |

|         | <image/> <image/> <image/> <image/> <image/> | <image/> <image/>                        | <image/> <text></text>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Yale

**TEXAS** The University of Texas at Austin

#### First integration meeting summary

- Parallel tools

- Synchronous static timing analysis (STA) + asynchronous STA

- standalone tools

- no parasitics

- Asynchronous logic tools

- Compiler for pipelined asynchronous memory

- Preliminary 65nm and earlier process nodes

- ACT language and database

- Custom circuit design flow

- Simulation with hazard finding

- Netlist generation

- Layout versus schematic

- Xyce for analog simulation

E.g: dot product engine, simple µcontroller

#### Second integration meeting summary

- Parallel tools

- \* SPRoute: a parallel global router (to appear, ICCAD 2019)

- Timer

- Inner loop of buffer insertion + gate sizing (3rd place, TAU contest 2019)

- Re-architected: netlist, delay calculator, parasitics abstracted out

- Integrated with async database (ACT)

- Asynchronous logic tools

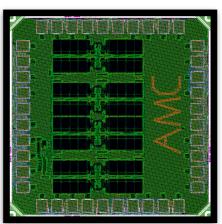

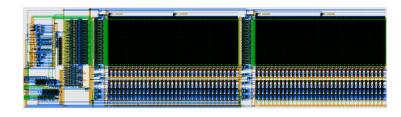

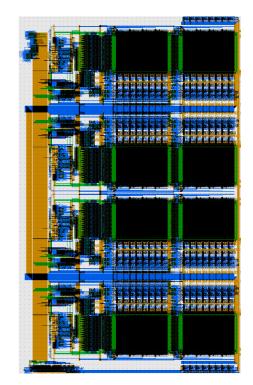

- \* AMC: async memory compiler (ASYNC 2019, Best paper finalist)

- Built-in self-test (BIST) support

- 28nm support and 65nm test chip

- Preliminary place and route flow

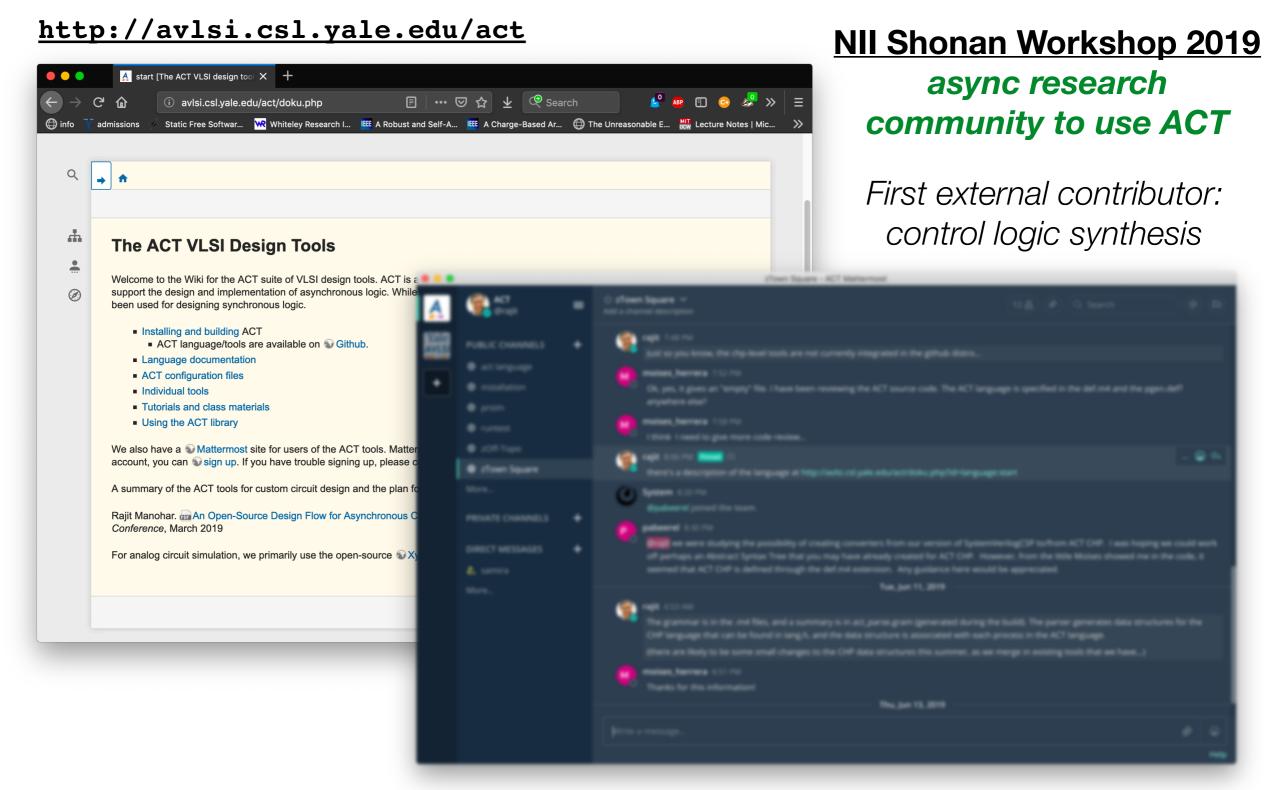

- Community support

- GitHub

<u>http://github.com/asyncvlsi/{act, AMC}</u>

<u>http://avlsi.csl.yale.edu/act/</u>

<u>http://github.com/IntelligentSoftwareSystems/Galois</u>

#### update

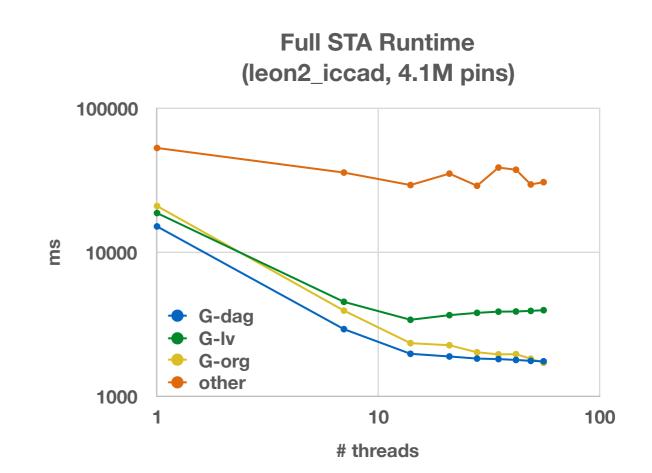

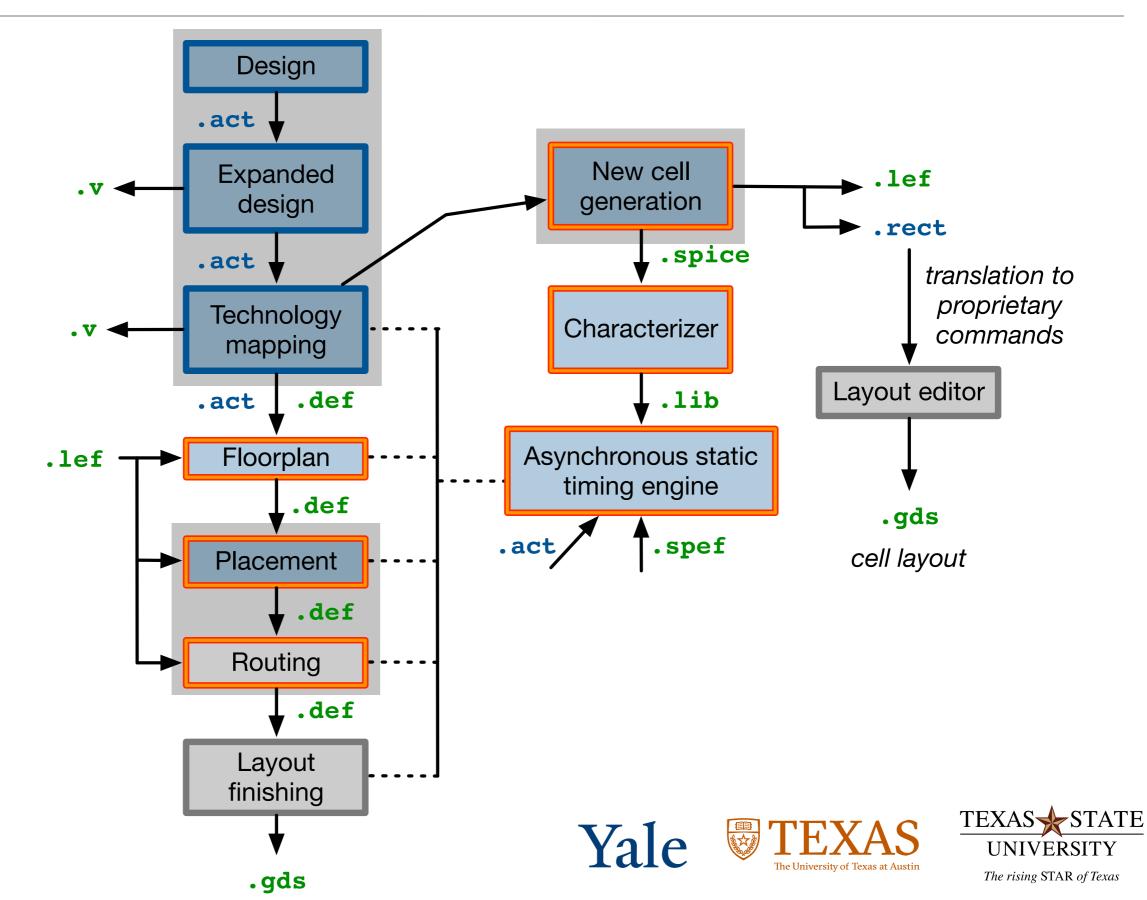

## Parallel static timing analysis

- Parallel STA for synchronous logic

- Supports parasitics (.spef)

- Used as core library in gate sizing

- Refactored to be integration-ready

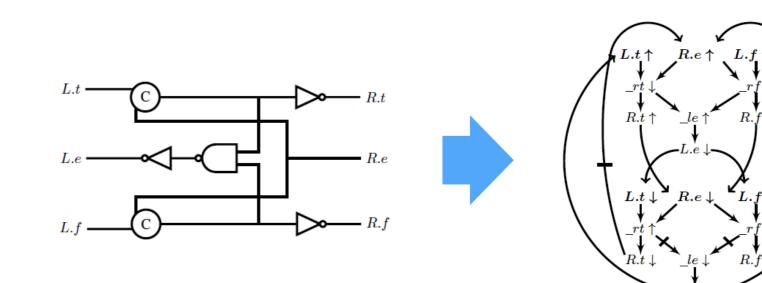

- Parallel STA for asynchronous logic

- Inherits features of new STA core

- Integrated with ACT database (was: Verilog + timing arcs file)

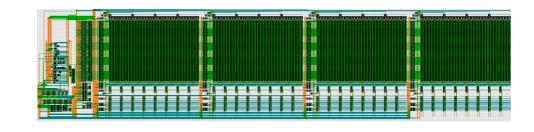

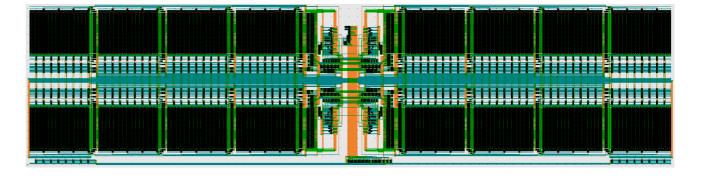

## **AMC: Asynchronous Memory Compiler**

- Features

- New command: read-modify-write

- Banking

- Sub-banking for better power/ performance at area cost

- Flexible orientation

- Updates

- \* 1st version on Github (May 2019)

- Built-in self-test (BIST) engine

- ✤ 65nm tape-out

- Thin-cell layout, min area, asymmetric vias

- ✤ 28nm generator with foundry cells

| Words | Bits | Bank | Area (um²) | Perf. (GHz) | Power (uW/MHz) | Leakage (uW) |

|-------|------|------|------------|-------------|----------------|--------------|

| 256   | 8    | 1    | 2744       | 2.4         | 1.02           | 2.45         |

| 512   | 8    | 1    | 3145       | 2.1         | 1.22           | 2.70         |

| 1024  | 8    | 2    | 7410       | 1.8         | 2.36           | 3.95         |

| 8192  | 8    | 4    | 49010      | 2.2         | 3.60           | 13.80        |

update

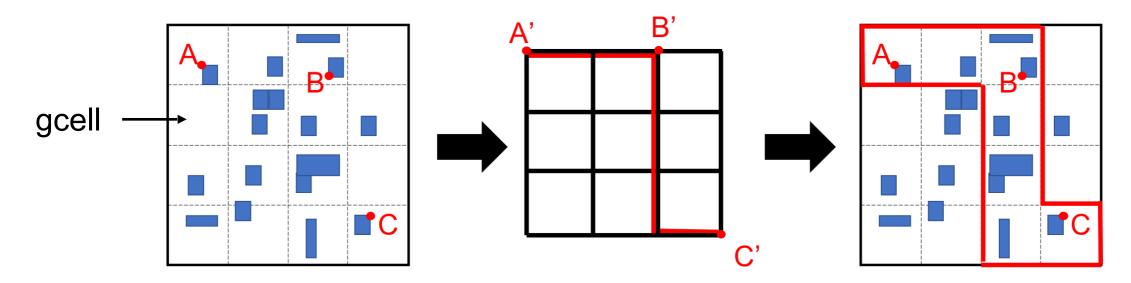

#### **Parallel global router**

The global routing partitions the chip area and forms a grid graph

- The **capacity** of an edge: the number of routing tracks available between two adjacent gcells.

- The **overflow** of an edge: the number of wires that exceeds the capacity.

The global routing problem: For every input net, to find a route that connects all the pins of the net on the grid graph.

Constraint: No overflow (routability).

UNIVERSITY

The rising STAR of Texas

Objectives: Minimize the total wire length and the number of vias.

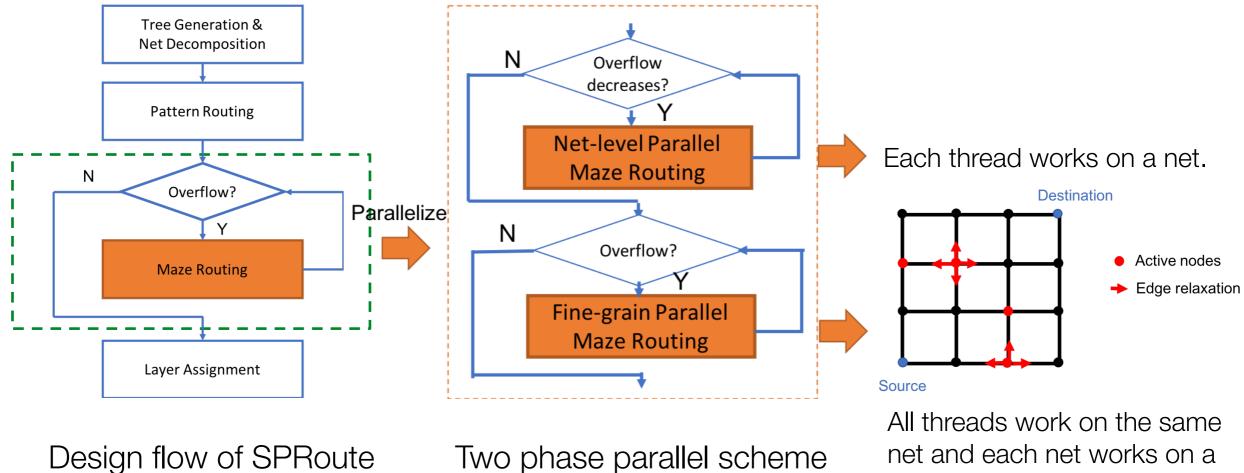

#### **Parallel global router: SPRoute**

- SPRoute: A Scalable Parallel Negotiation-based Global Router

- ✤ To appear, ICCAD 2019

- Exploit nested parallelism and solve the live-lock issue by a novel hybrid parallelization scheme.

Two phase parallel scheme

net and each net works on a work item of the frontier

#### Parallel global router: SPRoute

- SPRoute is implemented in C++ on Galois 4.0; builds on FastRoute

- We evaluate SPRoute on

- \* ISPD 2008 benchmark suite

- \* A 28-core Intel Xeon Gold machine

- Compare with FastRoute 4.1 and NCTU-gr 2.0. (Normalized to SPRoute)

| Overflow-free Cases (11 benchmarks) |         |               |                  |                     |  |

|-------------------------------------|---------|---------------|------------------|---------------------|--|

|                                     | SPRoute | FastRoute 4.1 | NCTU-gr 2.0 Fast | NCTU-gr 2.0 Regular |  |

| Wirelength                          | 1.0     | 0.994         | 1.024            | 0.999               |  |

| #Vias                               | 1.0     | 0.984         | 1.085            | 1.022               |  |

| Time                                | 1.0     | 11.0          | 8.4              | 10.0                |  |

| Hard-to-route Cases (4 benchmarks)  |         |               |                  |                     |  |

|                                     | SPRoute | FastRoute 4.1 | NCTU-gr 2.0 Fast | NCTU-gr 2.0 Regular |  |

| Total overflow                      | 1.0     | 0.930         | 5.17             | 2.477               |  |

| Wirelength                          | 1.0     | 0.994         | 1.03             | 0.997               |  |

| #Vias                               | 1.0     | 0.989         | 1.03             | 0.998               |  |

| Time                                | 1.0     | 3.1           | 0.37             | 80.1                |  |

#### **Digital flow**

new

#### Community

#### new

Yale

Known users: 9 academic groups; 4 companies

#### Come talk to us!

|         | Asynchronous<br>design & tools | Parallel data-structures<br>& algorithms | GPU-based parallelization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------|--------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Faculty | Fajit Manohar<br>(Yale)        | Keshav Pingali      (UT Austin)          | With the second seco |

| C       | <image/> <image/>              | <image/> <image/> <caption></caption>    | <image/> <image/> <text></text>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.