# AMS Emulation Technology Results From DARPA POSH – Phase 1

Chris Tice, VP Verification Continuum Solutions and Manufacturing Oleg Raikhman, Solutions Architect Yishai Statter, R&D Engineer

July 2019

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions, and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government."

### What is this?

Or ....

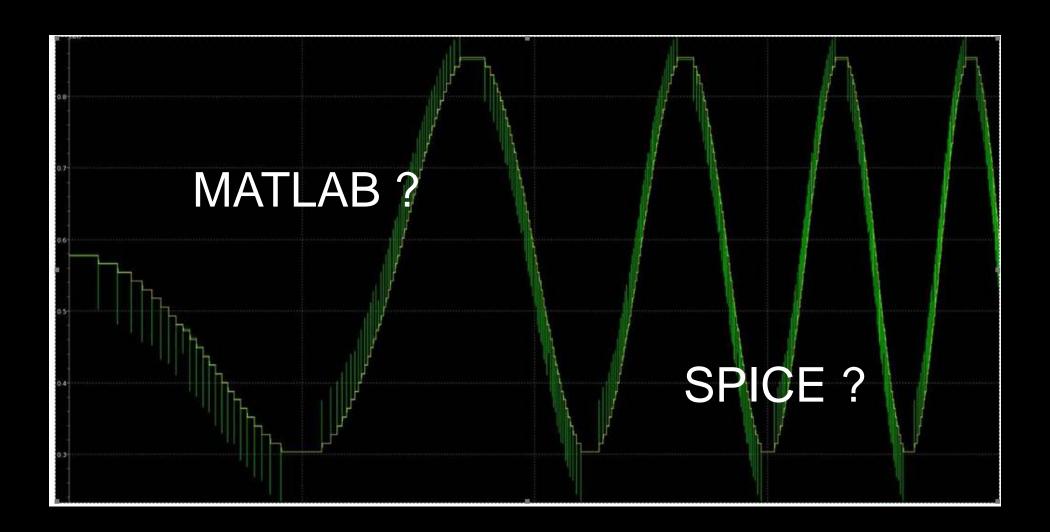

# **AMS Verification Today**

Too Slow for Software and System Validation

- Engine

- Analog Mixed-Signal Simulation (SPICE + SV)

- Advantage

- Accuracy

- Disadvantage

- Slow

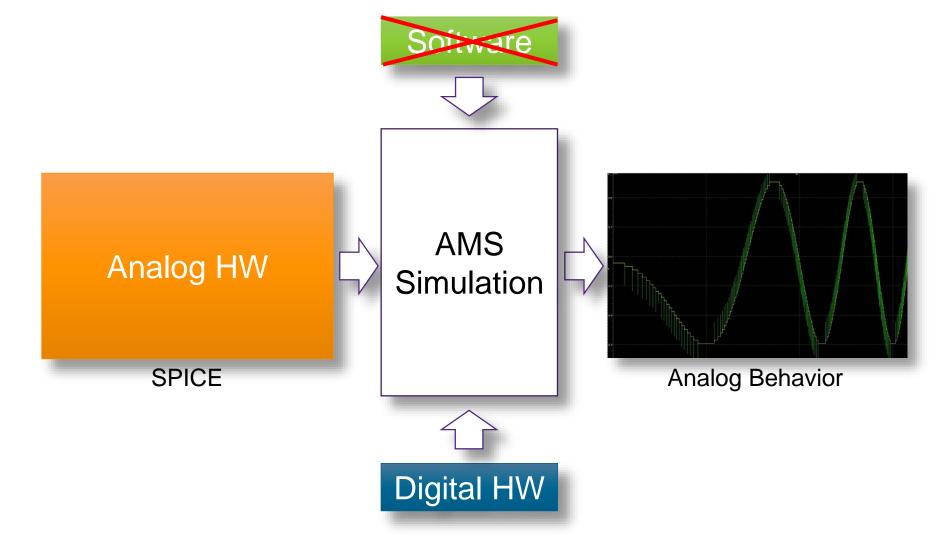

### What's Needed

### System and Software Validation for AMS Designs

- Engine

- Ability to execute software workloads

- Modeling

- Using standard language

- Accuracy

- Sufficient for system level integration analysis

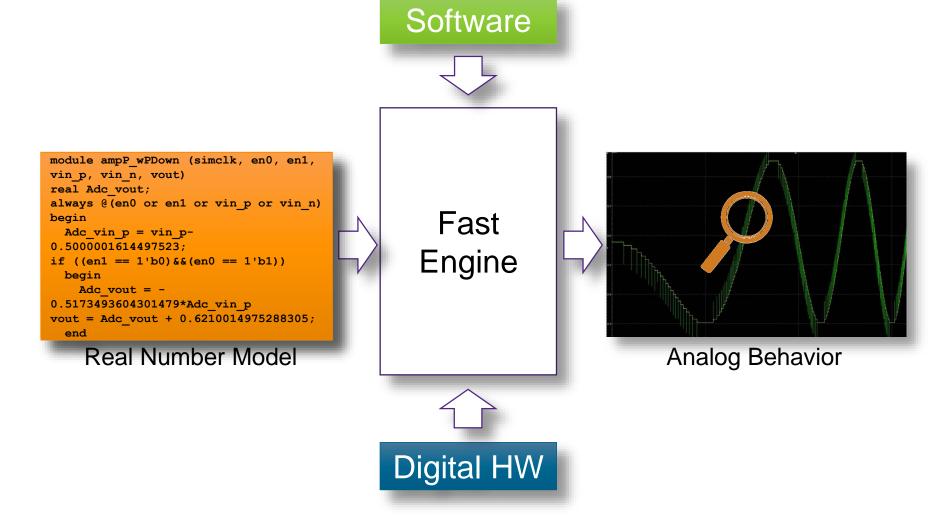

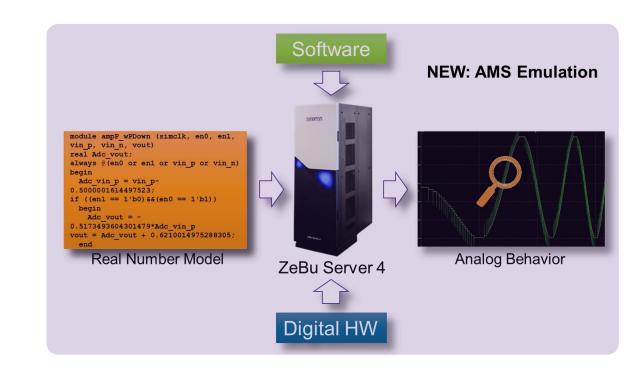

### DARPA POSH – Phase 1 Result: AMS Emulation

### System and Software Validation for AMS Designs

- Engine

- Emulation

- Modeling

- Real Number Model using SV data type

- Accuracy

- Sufficient for system level integration analysis

### Demo Time: Let's Take a Quick Look

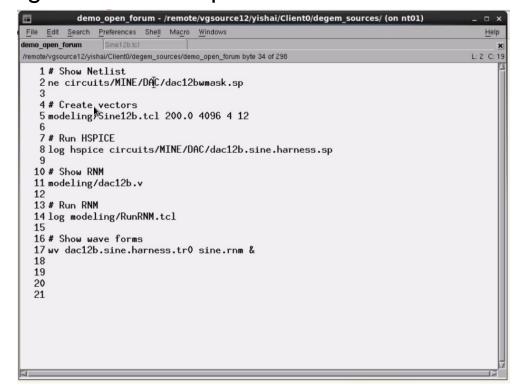

# SPICE Conversion to RNM Demonstration (1)

#### **FLOW**

We will display the input netlist (a mix of digital and analog content), show how the tool recognizes and separates this content, run SPICE, convert the netlist to RNM and display it (takes only 1 second to simulate RNM vs. 70 for SPICE), and compare the simulation output of SPICE input against RNM output

# SPICE Conversion to RNM Demonstration (2)

### Snippet of DAC SPICE netlist

```

dac12bwmask.sp - /remote/vgsource12/yishai/Client0/degem_sources/circuits/MINE/DAC/ (on nt01)

File Edit Search Preferences Shell Macro Windows

remote/vgsource12/yishai/Client0/degem_sources/circuits/MINE/DAC/dac12bwmask.sp byte 0 of 6381

L: 1 C: 0

76 r9 p9 p9t 2e4

77 ra9 pat p9t 1e4

78 ra pa pat 2e4

79 rab pat out 1e4

80 rb pb out 2e4

81 .ends

83 .subckt opamp gnd wdd vin_n vin_p vout

84 r0 yout vin n 5e9

85 r1 ibias net030 1.9141e3 M=1

86 mt1 net065 vin_p net020 vdd fetp L=1e-6 W=8e-6 AD=2.24e-12 AS=3.84e-12 PD=560e-9

87 mn1 net020 net085 vdd vdd fetp L=1e-6 W=10e-6 AD=5.6e-12 AS=7.6e-12 PD=1.12e-6 P

88 mn0 net085 net085 vdd vdd fetp L=1e-6 W=10e-6 AD=5.6e-12 AS=7.6e-12 PD=1.12e-6 P

89 mt2 vout vin_n net020 vdd fetp L=1e-6 W=8e-6 AD=2.24e-12 AS=3.84e-12 PD=560e-9 P

90 mp0 ibias ibias gnd gnd fetn L=2e-6 W=10e-6 AD=2.8e-12 AS=4.8e-12 PD=560e-9 PS=2

91 mp3 net085 ibias gnd gnd fetn L=2e-6 W=10e-6 AD=2.8e-12 AS=4.8e-12 PD=560e-9 PS=

92 mp2 vout net065 gnd gnd fetn L=2e-6 W=2e-6 AD=560e-15 AS=960e-15 PD=560e-9 PS=4.

93 mt4 ibias vdd gnd gnd fetn L=1e-6 W=5e-6 AD=1.2e-12 AS=1.2e-12 PD=5.48e-6 PS=5.4

94 mp1 net065 net065 gnd gnd fetn L=2e-6 W=2e-6 AD=560e-15 AS=960e-15 PD=560e-9 PS=

95 .ends opamp

97 .subckt switch s out a0 a1 vdd gnd

98 xinv s sb vdd gnd inv

99 mp0 out s a0 vdd fetp L=1e-6 W=40e-6 AD=2.24e-12 AS=3.84e-12 PD=560e-9 PS=16.96e

100 mn0 out sb a0 gnd fetn L=1e-6 W=20e-6 AD=2.8e-12 AS=4.8e-12 PD=560e-9 PS=20.96e-

101 mp1 out sb a1 vdd fetp L=1e-6 W=40e-6 AD=2.24e-12 AS=3.84e-12 PD=560e-9 PS=16.96

102 mn1 out s a1 gnd fetn L=1e-6 W=20e-6 AD=2.8e-12 AS=4.8e-12 PD=560e-9 PS=20.96e-6

103 .ends

```

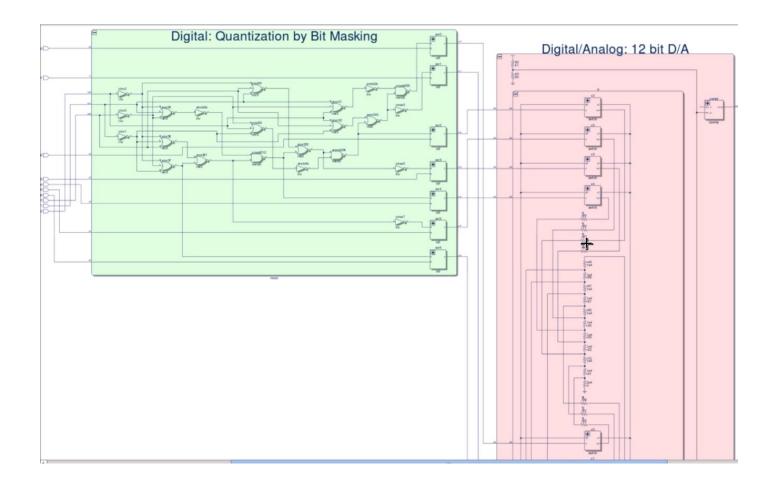

# SPICE Conversion to RNM Demonstration (3)

SPICE conversion tool recognizes and separates digital and analog circuits

# SPICE Conversion to RNM Demonstration (4)

SPICE simulation takes 70 seconds (RNM takes 1 second)

```

File Edit View Search Terminal Help

# nodes

384 # elements =

# resistors =

31 # capacitors =

1 # inductors =

# mutual inds =

0 # vccs

0 # vcvs

# cccs

0 # ccvs

0 # volt srcs =

15

# curr srcs =

0 # diodes =

# ifets

0 # mosfets =

81 # U elements =

# T elements =

# S elements =

0 # va device =

# vector srcs =

0 # N elements =

****** Runtime Statistics (seconds) ******

# points tot. iter conv.iter

analysis

op point

0.01

1

26

68.52

20001

319429

220492 rev=

15005

transient

readin

0.72

errchk

0.07

setup

0.01

output

peak memory used

556.14 megabytes

total cpu time

69.@DURATION seconds

total elapsed time

70.@DURATION seconds

job started at

14:28:00 06/27/2019

job ended at

14:29:10 06/27/2019

***** hspice job concluded

lic: Release hspice token(s)

lic: total license checkout elapse time:

0.74(s)

otal run time: 70 seconds

```

# SPICE Conversion to RNM Demonstration (5)

Snippet of RNM generated (note mix of digital Boolean and analog real numbers)

```

dac12b.v - /remote/vgsource12/yishai/Client0/degem_sources/modeling/ (on nt01)

_ 🗆 ×

File Edit Search Preferences Shell Macro Windows

/remote/vgsource12/yishai/Client0/degem_sources/modeling/dac12b.v byte 0 of 1086

L: 1 C: 0

11 input i5;

12 input i6;

13 input a7:

14 input a8:

15 input a9:

16 input aa;

17 input ab;

wire a6=i61m0&m1&m2

wire a5=i5|m1&m2;

wire a4=~m0&(i4|m1&m2)|(i4|m2)&m0;

wire a3-i31m2;

wire a2 2 m2&m0&m1li2lm2

wire al=i1|m1|m2:

24 wire a0=~m1&~m2&m0|i0|m1|m2:

25 real conversion:

26 output real out;

27 always @(*) begin

29

(ab ? -0.38170738623046835 : 0)+\

30

(aa ? -0.19168871142578098 : 0)+\

31

(a9 ? -0.09636313037109301 : 0)+\

(a8 ? -0.04847353076171851 : 0)+\

33

(a7 ? -0.024415115722657033 : 0)+\

34

(a6 ? -0.012302542480469802 : 0)+\

37

(a3 ? -0.001559899902343842 : 0)+\

(a2 ? -0.0007908530273444958 : 0)+\

```

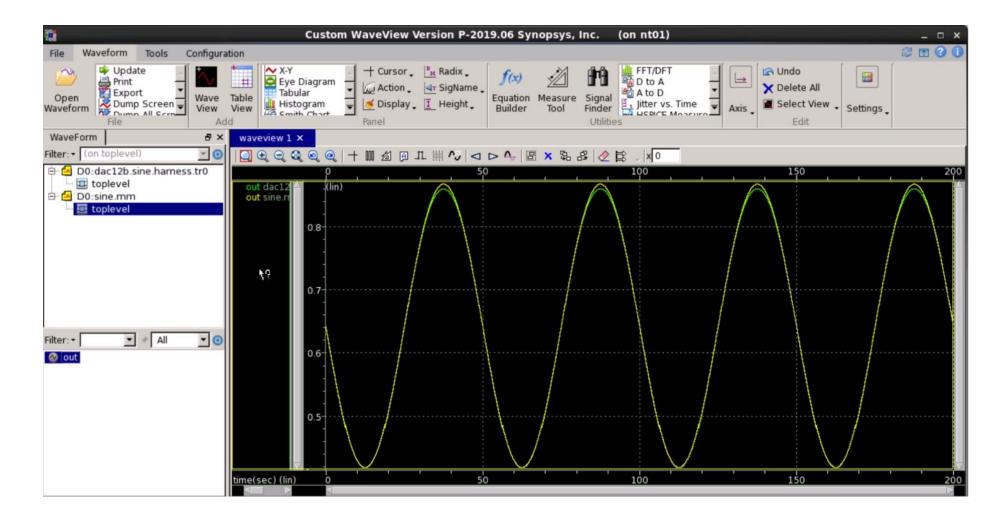

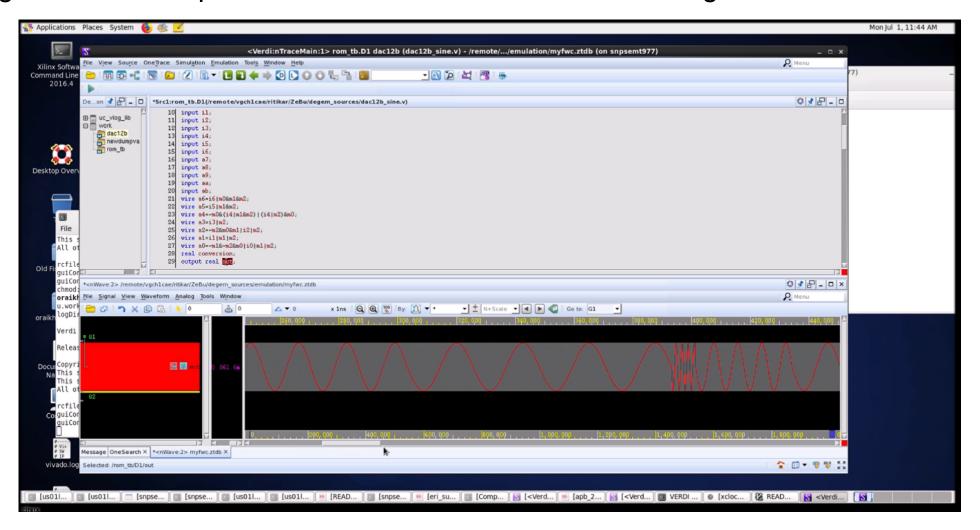

# SPICE Conversion to RNM Demonstration (6)

Comparison of SPICE vs. RNM simulation output waveforms

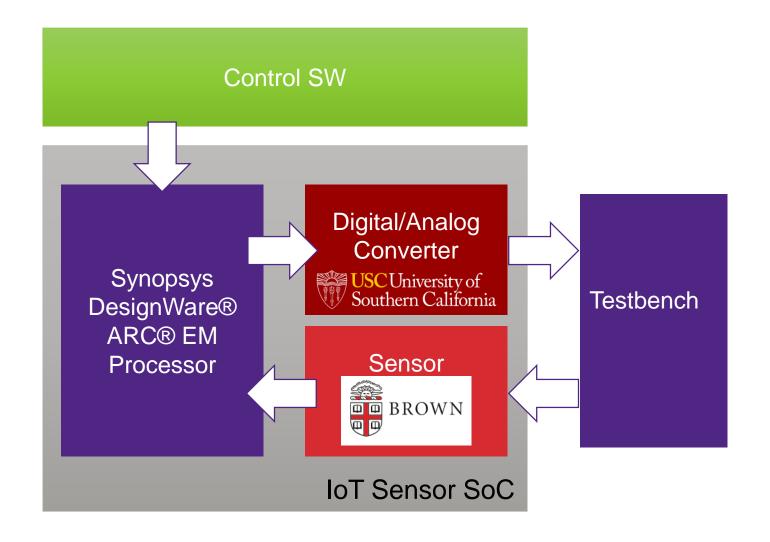

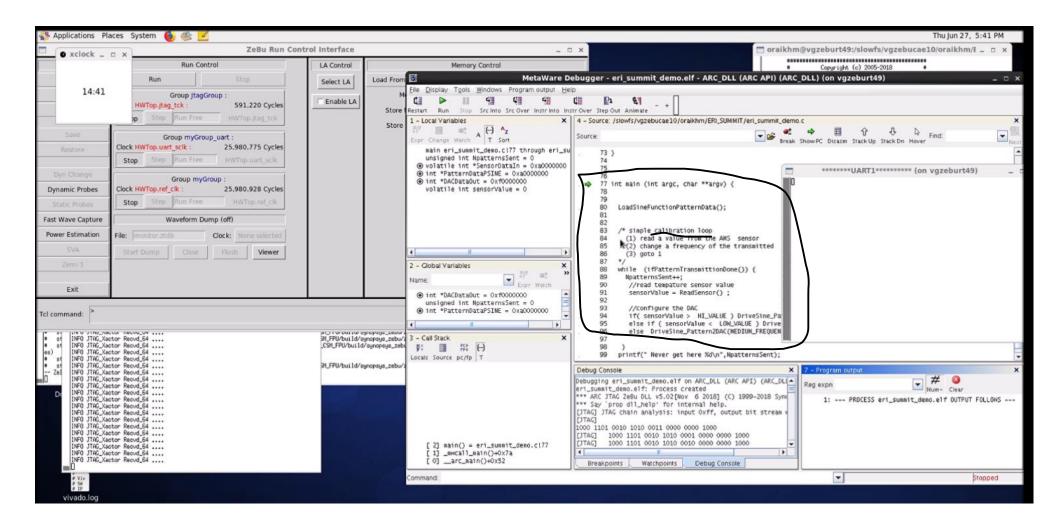

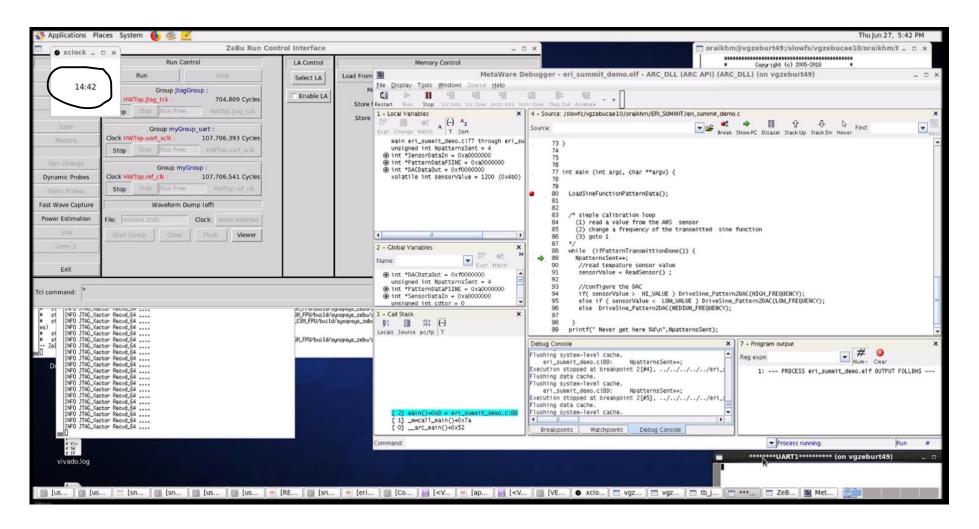

# AMS Emulation (1)

Debugger at breakpoint showing calibration software running on ZeBu emulator

# AMS Emulation (2)

At 2:42 PM, remove breakpoint and let emulator run (@ 2 MHz)

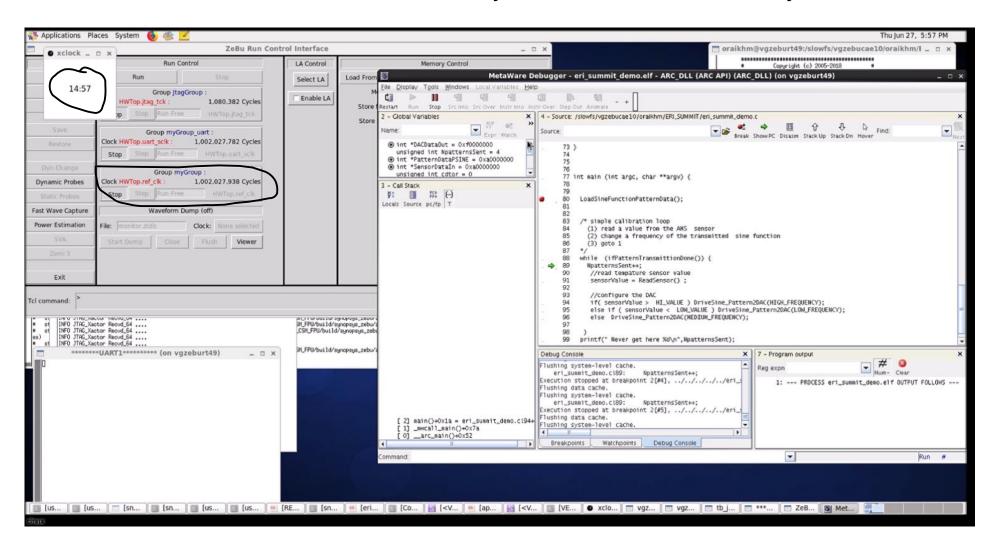

# AMS Emulation (3)

At 2:57 PM, 15 seconds later, have already run over one billion cycles

# AMS Emulation (4)

Analog waveform output from simulator shows circuit working

# AMS Emulation: Summary and Next Steps

#### Results From DARPA POSH – Phase 1

- What you saw today

- AMS emulation is working

- AMS emulation delivers expected performance

- Validation of AMS SoC including SW

- Next Steps

- Continue to optimize AMS emulation technology

- Enlarge the AMS emulation partner community

- Develop complementary AMS assertions

# Thank You

The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.