#### **ERI Design: USC POSH**

### Automated Analog Mixed Signal (AMS) IP generator for CMOS technologies

FA8650-18-2-7853

Under contract June 25, 2018. Phase IA completed June 24, 2019

Mohsen Hassanpourghadi, Qiaochu Zhang, Praveen Sharma, Jaewon Nam, Shiyu Su, Subhajit Chowdhury, Jagannathan Sathyamoorthy, Walter Unglaub, Mutian Zhu

Tony Levi, Mike Chen, Sandeep Gupta

University of Southern California

ERI Detroit meeting

3.40pm, Wednesday July 17, 2019

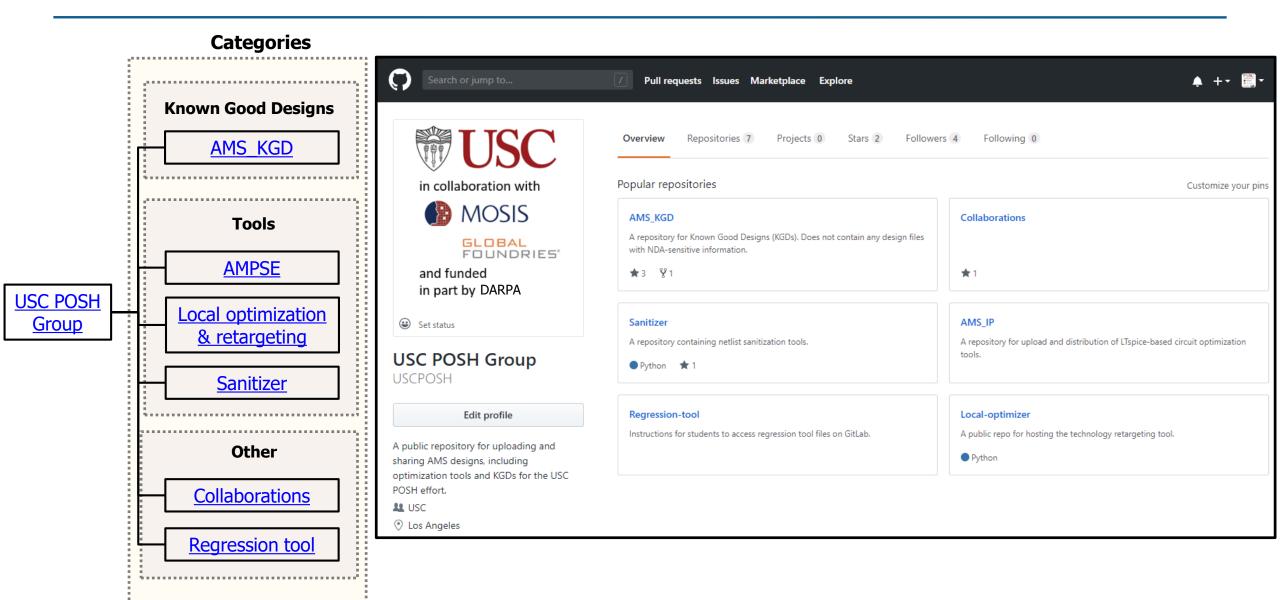

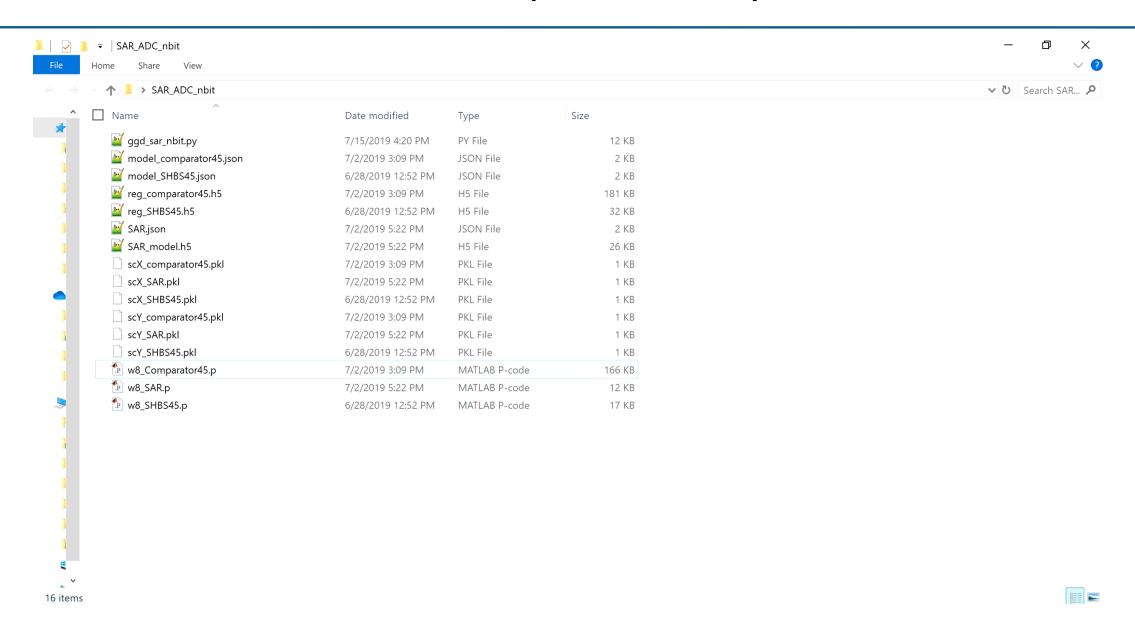

# Public open-source USC POSH repository, <a href="https://github.com/USCPOSH">https://github.com/USCPOSH</a>

4-----

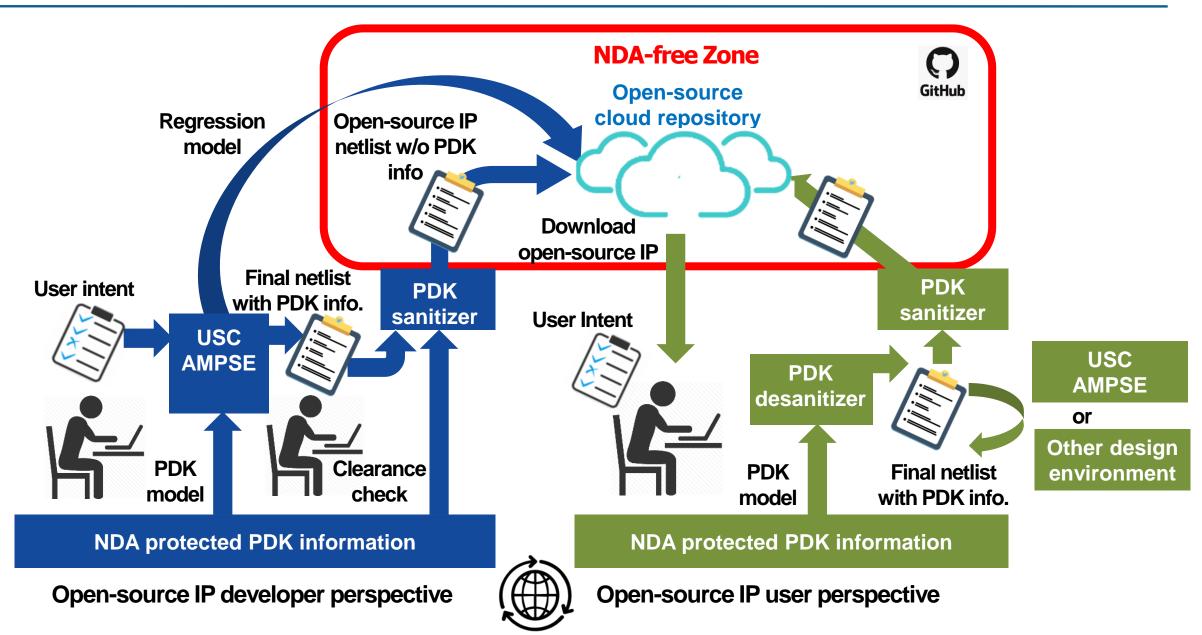

#### Traversing NDA-protected and NDA-free zones

# Public open-source USC POSH repository, <a href="https://github.com/USCPOSH">https://github.com/USCPOSH</a>

#### Traversing NDA-protected and NDA-free zones with sanitization

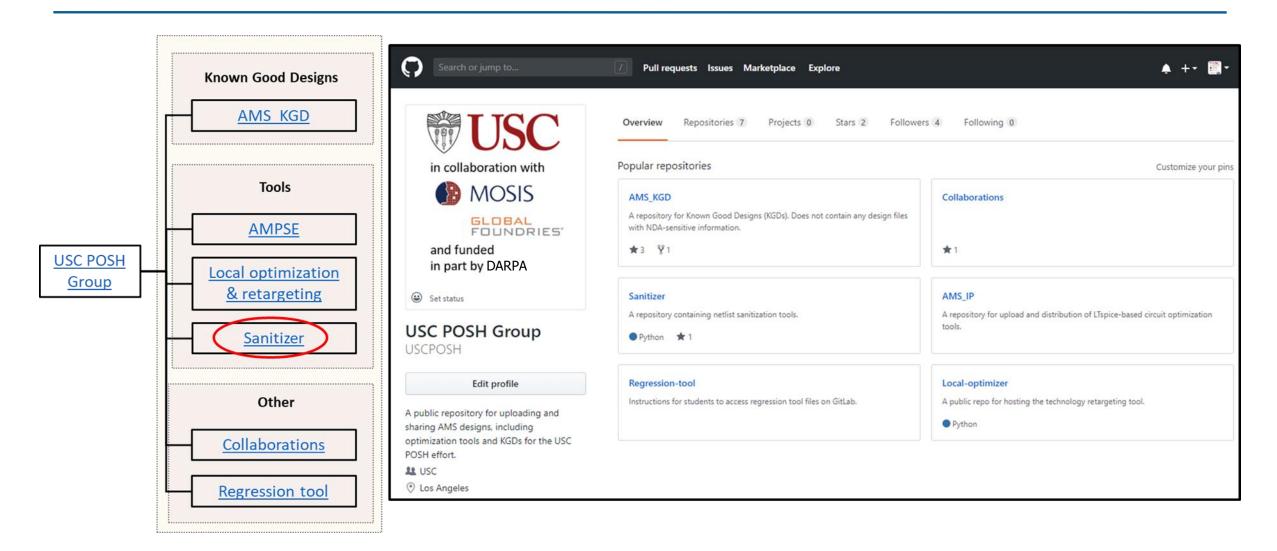

#### **Sanitization**

#### **Netlist with PDK information (GF65)**

# Eliminating PDK information (NMOS / PMOS)

#### **Sanitized Netlist**

```

subckt INV65_v1 IN OUT VDD VSS

M1 ( OUT IN VDD VDD ) p### l=lppp w=wppp*mp m=1 nf=mp

M0 ( OUT IN VSS VSS ) n### l=linnn w=winnn*mn m=1 nf=mn

ends INV65 v1

```

#### **Desanitization**

#### **Sanitized Netlist**

```

subckt INV65_v1 IN OUT VDD VSS

M1 ( OUT IN VDD VDD ) p### l=lppp w=wppp*mp m=1 nf=mp

M0 ( OUT IN VSS VSS ) n### l=linnn w=winnn*mn m=1 nf=mn

ends INV65 v1

```

Adding PDK information necessary for accurate simulations

#### **Netlist with PDK information**

### Public open-source USC POSH repository, <a href="https://github.com/USCPOSH">https://github.com/USCPOSH</a>

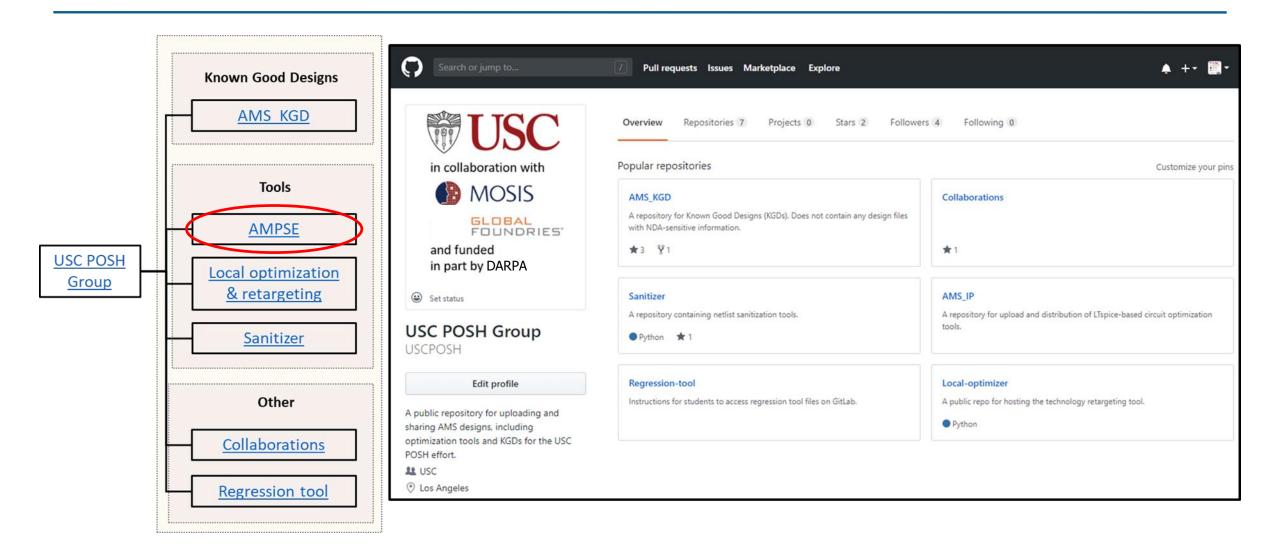

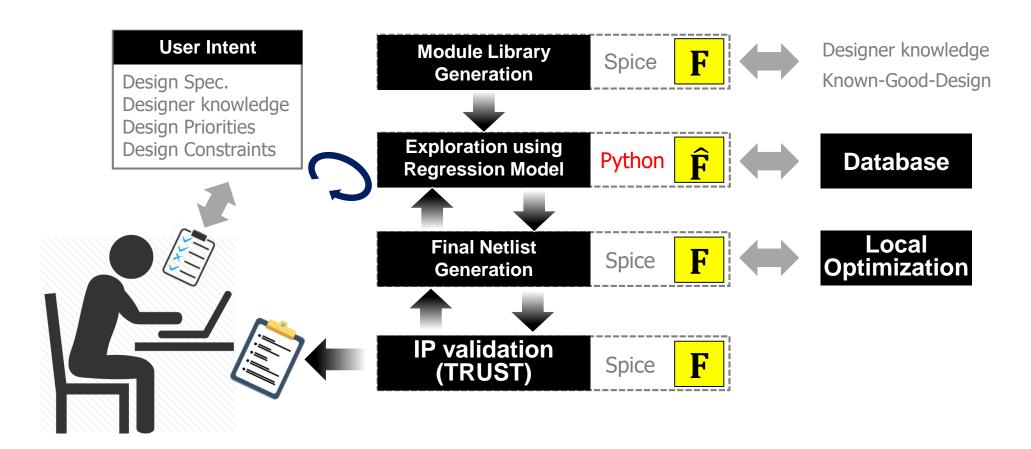

### Analog Mixed-signal Parameter Search Engine (AMPSE) Design Flow

Expand AMS Design Space beyond single specification/technology for open-source (including Xyce) ecosystem

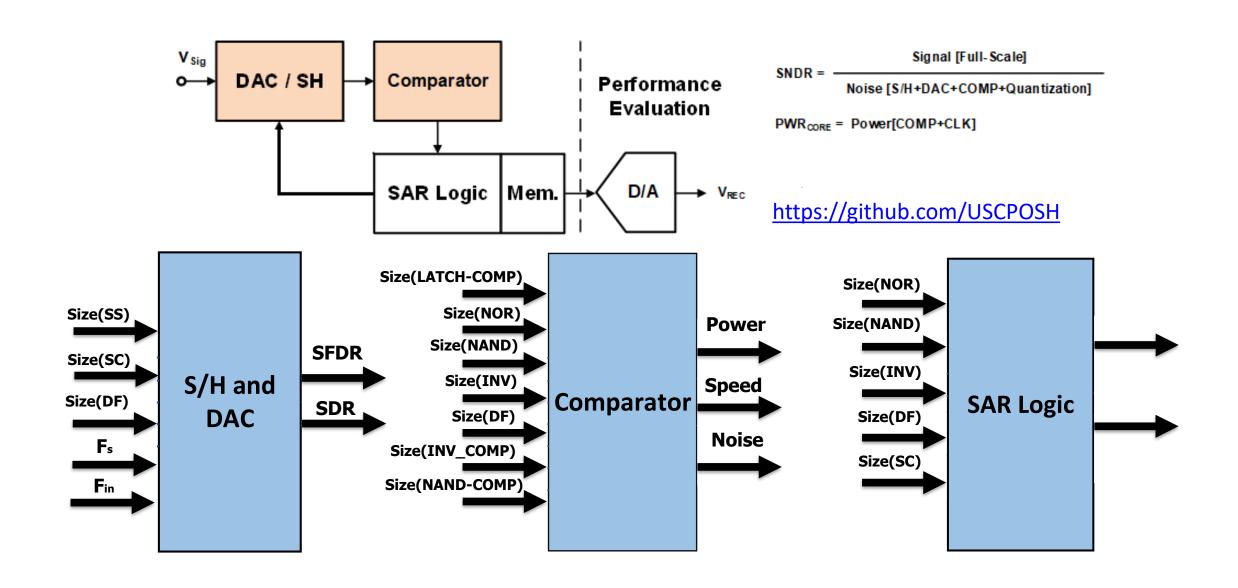

#### AMPSE design: SAR ADC

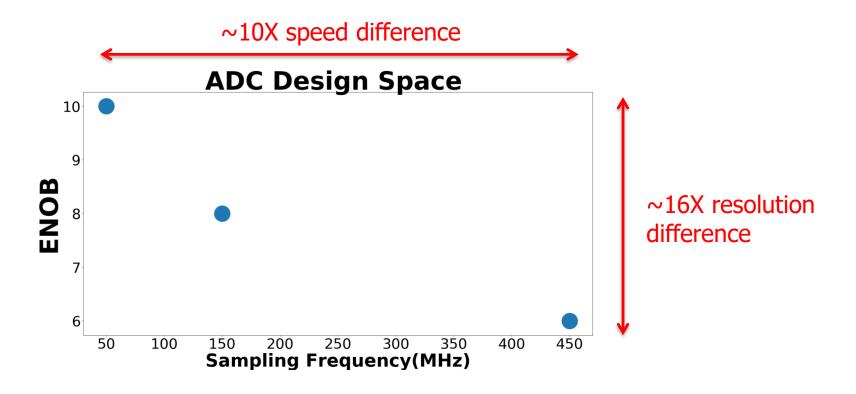

#### Access broad range of design objectives

#### Let's try these...

- 50MS/s 10-bit SAR ADC

- 150MS/s 8-bit SAR ADC

- 450MS/s 6-bit SAR ADC

(1)

$$\sum T_{COMP,k} + (N-1)\cdot Max\{T_{RS}, T_{DAC}\} < 75\%$$

Tperiod

- (2) SFDR > SFDR<sub>target</sub>

- (3) SNDR > SNDR<sub>target</sub>

(4) ...

Formulate corresponding constraints function for AMPSE

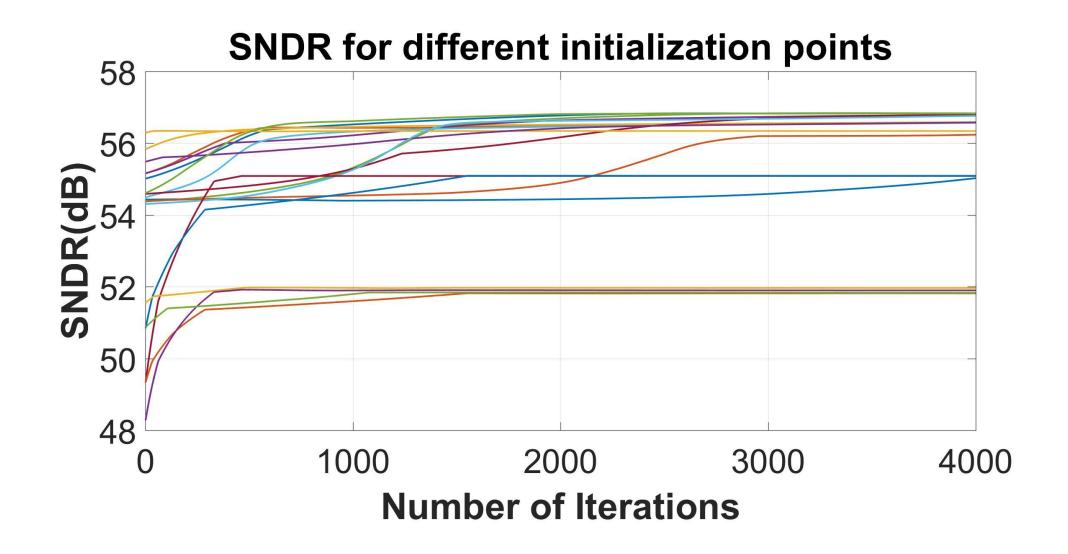

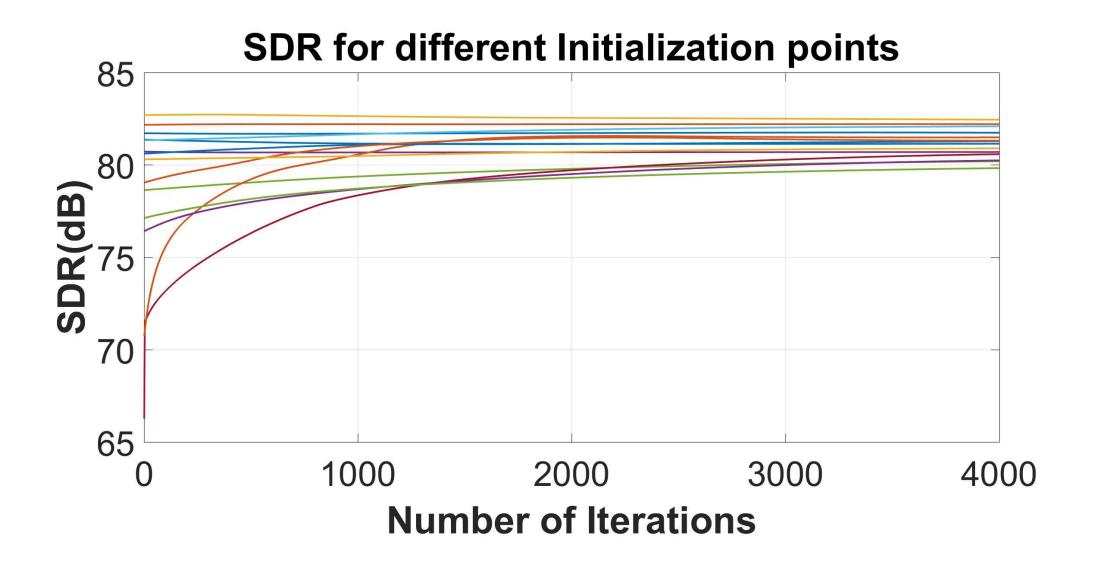

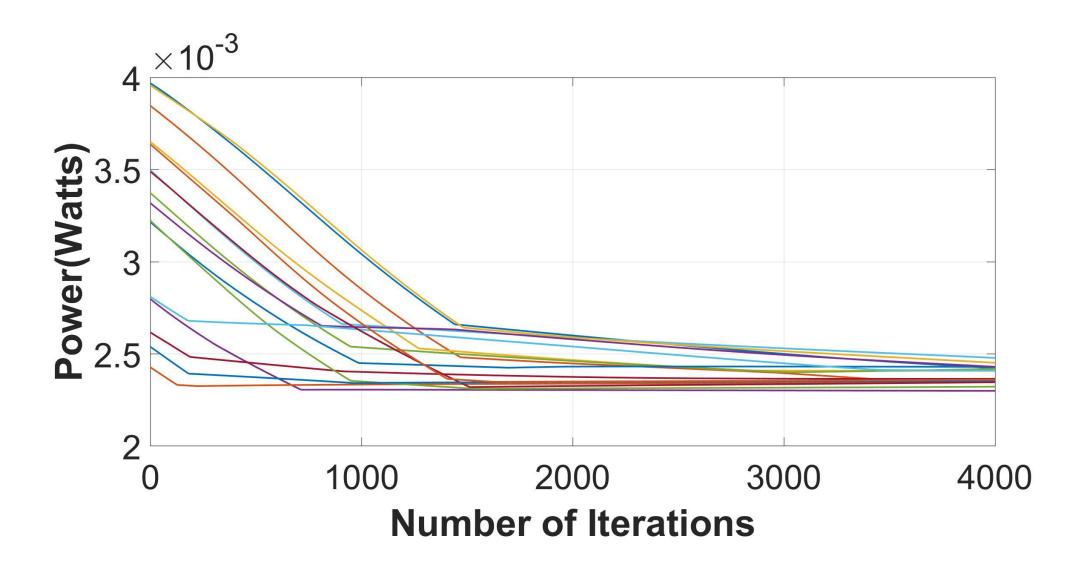

### Use AMPSE for 10-bit ADC (schematic level)

### SPICE validation of AMPSE design (schematic level)

#### • 50MS/s, 10-bit SAR ADC

| Performance Metric | AMPSE design       | SPICE Simulation |

|--------------------|--------------------|------------------|

| ENOB               | 9.14               | 8.5              |

| SFDR               | 80.7dB(T/H Module) | 60.15dB          |

| Power Consumption  | 2.4mW              | 3.8mW            |

#### • 150MS/s, 8-bit SAR ADC

| Performance Metric | AMPSE design        | SPICE Simulation |

|--------------------|---------------------|------------------|

| ENOB               | 7.9                 | 7.6              |

| SFDR               | 70.76dB(T/H Module) | 54.12dB          |

| Power Consumption  | 4.43mW              | 6.7mW            |

#### • 450MS/s, 6-bit SAR ADC

| Performance Metric | AMPSE design       | SPICE Simulation |

|--------------------|--------------------|------------------|

| ENOB               | 5.9                | 5.3              |

| SFDR               | 58.2dB(T/H Module) | 41.2dB           |

| Power Consumption  | 10.9mW             | 12.6mW           |

#### **ERI Design: USC POSH**

### Automated Analog Mixed Signal (AMS) IP generator for CMOS technologies

FA8650-18-2-7853

Under contract June 25, 2018. Phase IA completed June 24, 2019

# USC POSH repository, <a href="https://github.com/USCPOSH">https://github.com/USCPOSH</a>

**ERI** Detroit meeting

3.40pm, Wednesday July 17, 2019

The views, opinions and/or findings expressed are those of the authors and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.