# Heterogeneous Systems-on-Wafers

Siva Jangam, Boris Vaisband, and Subramanian S. Iyer University of California, Los Angeles

## 3D Heterogeneous Integration: Common Heterogeneous Integration and IP Reuse Strategies (CHIPS)

—With apologies to Gordon Moore

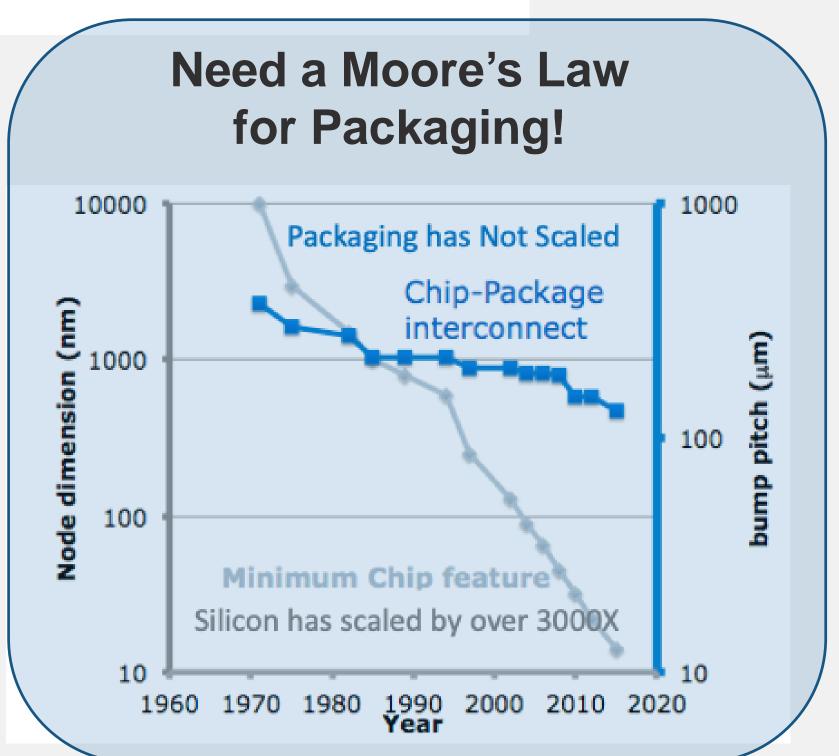

Early attempts at monolithic Wafer-Scale-Integration failed mainly due to yield limitations Lets revisit this problem using advanced packaging and build Heterogeneous Wafer Scale Systems

#### Our approach:

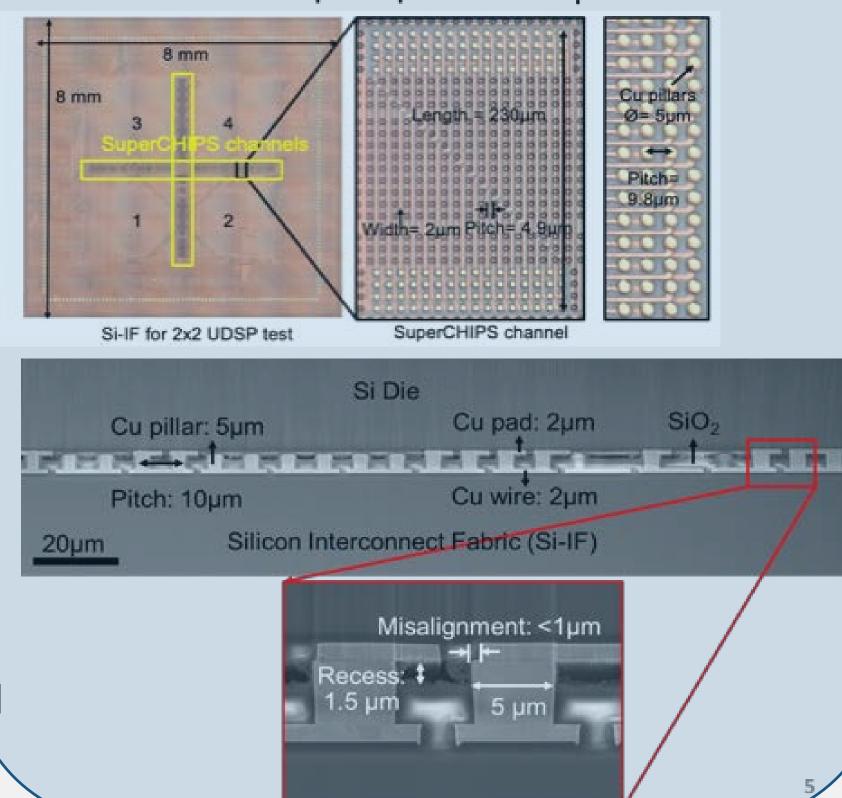

- Replace PCB with a silicon wafer with fine pitch wiring the Silicon Interconnect Fabric (Si IF)

- Assemble heterogeneous dielets on the SI IF at 2-10  $\mu$ m dielet-to-Wafer pitches (vs ~500  $\mu$ m)

- Place these dielets as close as possible to each other i.e. 20-100  $\mu$ m spacings (vs ~mm)

### You now have a Heterogeneous System-on-Wafer

#### **PCBs** vs. 3D/Interposer Si-IF VS. spacing: 20-100 μm Micro bumps < Heterogeneous Dielet 1 Heterogeneous dielet 2 Fine pitch 2-10 µm

- Multiple packaging levels

- Limited heat sinking

- Solder based interconnects

- Underfill needed

- Limited by BGA pitch

- PCB with and extra level

- Size limitation

- Needs expensive TSVs

- Interconnect pitch: 50 µm

- Thermal issues

- Single package level

- Excellent heat sinking

- Metal-metal interconnects

- No underfill

- Complete system integration

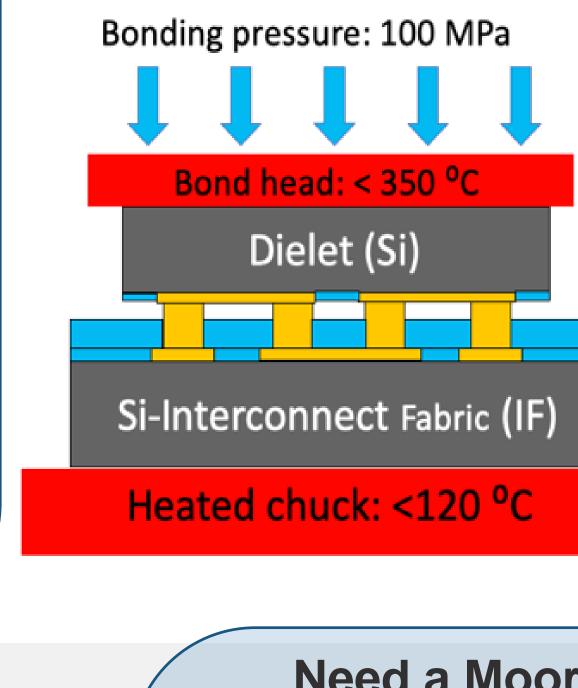

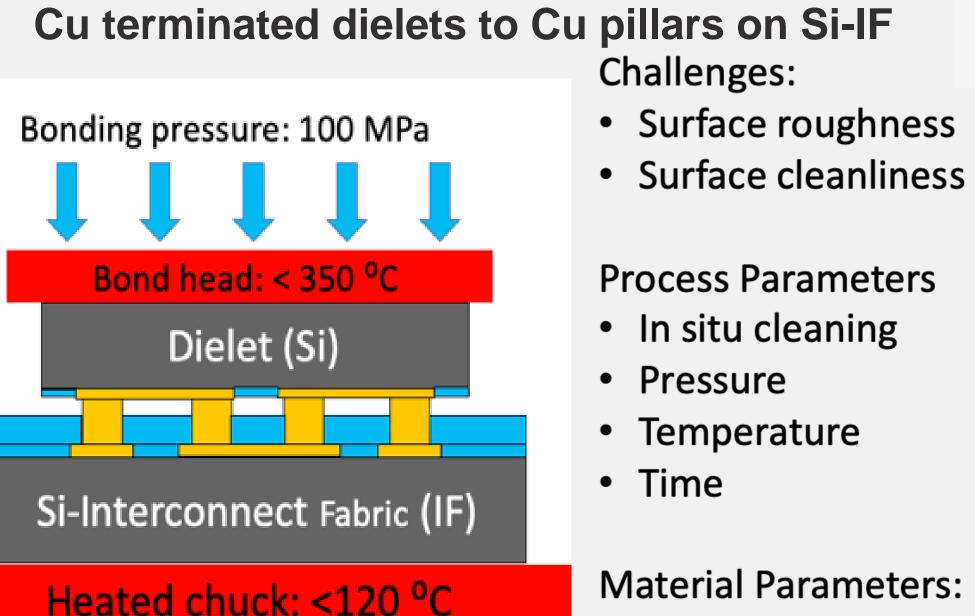

**Thermal Compression Bonding:**

Diffusivity

Plastic Deformation

#### CHIPS Optimal Dielet and Interconnect Pitch **Dielet size** Die yielding Mechanic constraint More reuse **Optimal** Electrical/logical pitch constraints\* constraints 2 to 10 μm SerDes-like **Optimal** dielet size/ SoC-like Packaging-like 1 to 81 mm<sup>2</sup> handling No reuse constraint **CMOS** wire-like 50 nm 500 μm Interconnect pitch BGA/LGA Gate pitch **Dielet/chiplet size (# of circuits)** I/O complexity/power - IP reuse **Testing complexity**

| Interconnect<br>pitch/protocol | 10 µm on Si-IF SuperCHIPS |                  | 50 µm on<br>Interposer | 400 µm on          | Improvement |

|--------------------------------|---------------------------|------------------|------------------------|--------------------|-------------|

|                                | Async                     | Sync             | HBM2                   | PCB/ SerDes        |             |

| No of links/mm                 | 200                       |                  | 20                     | 2.5                | 10-100X     |

| Latency (ps)                   | 35                        | 1 clock<br>cycle | 240[2]                 | ~1,000             | 7-30X       |

| Data-rate/link<br>(Gbps)       | 10                        | 4                | 2 <sup>[3]</sup>       | 64[1]              | 0.1-5X      |

| Energy/bit<br>(pJ/b)           | <0.04                     | <0.2             | 3.8 <sup>[2]</sup>     | 5.1 <sup>[1]</sup> | 20-120X     |

| Bandwidth/mm<br>(Gbps/mm)      | 8000*                     | 1600*            | 170 <sup>[3]</sup>     | 90                 | 10-100X     |

Si dielets on Si IF

InP dielets on Si IF

- Up to 4 Si IF wiring levels

- Pillar pitch 10μm legacy compatible (> 200µm)

- +/- 1 μm alignment

- Cu (Si dielets) or Au (III-V dielets) terminations - No Solder

- Both shear force and resistance better than BGAs

2 wiring levels & 4 rows of pillars =>Effective pillar pitch is <2.5μm

Small dielet integration on Si-IF enables:

- SoC performance (latency, bandwidth)

- >100x reduction in energy per bit

- Significantly reduced time to market

- 10-50X reduction in NRE

- IP reuse

- Heterogeneity

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.