## **Overview and Background**

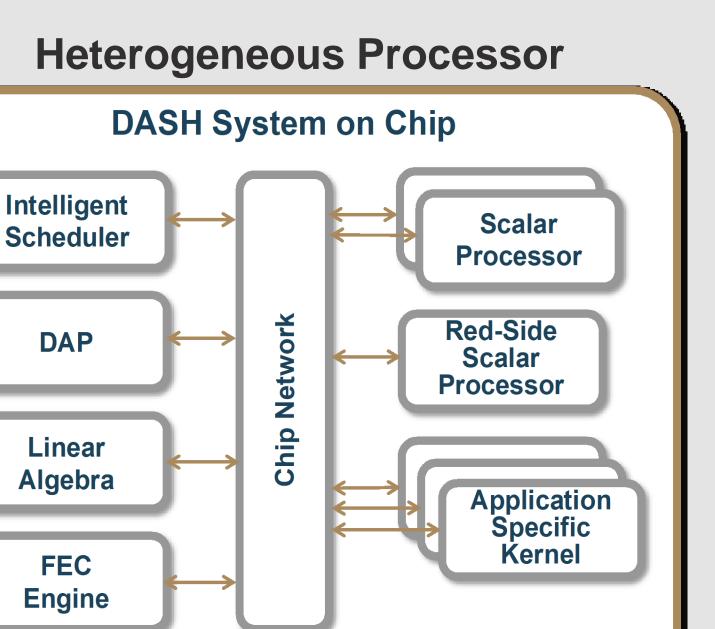

The DASH-SoC team drives flexible DSSoC computational systems that reduce SWaP numbers and also dramatically increase processing flexibility. We break the fundamental

**Domain-Focused** Advanced Heterogeneous SoC

trade that custom SoCs are required for power efficiency, but scalar processors are required for ease of implementation. <u>Goals</u>

The main goal is to develop a chip as computationally powerful as a custom ASIC, but also as flexible and easy to program as a scalar processor. Specific goals include:

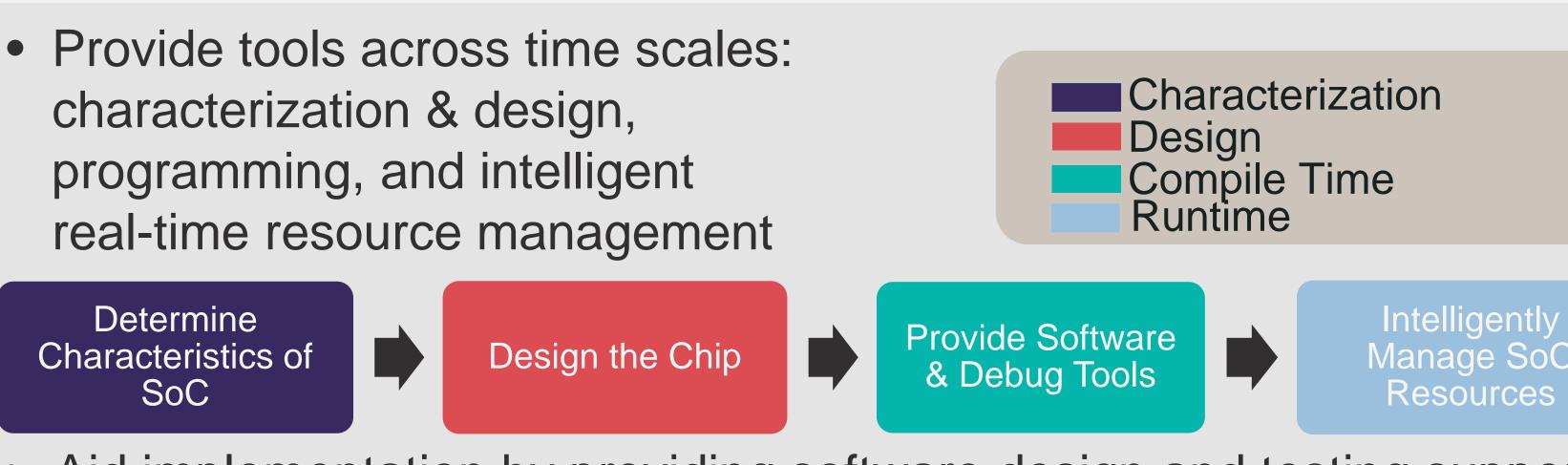

- Develop tools to design and use heterogenous processor for a range of signal processing applications

- Dramatically improve power efficiency

- Dramatically reduce engineering cost during SoC design and implementation

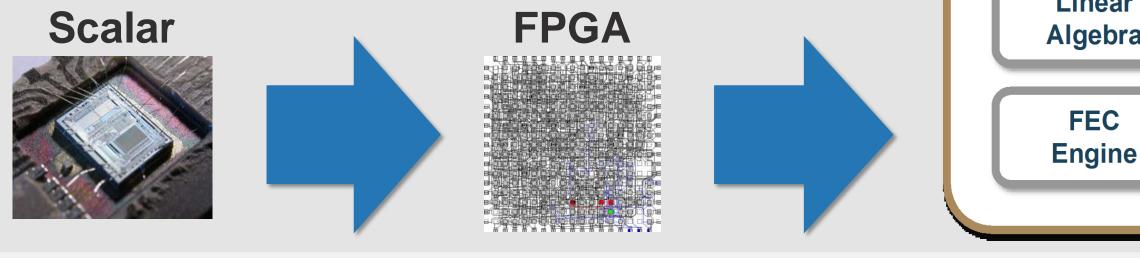

### **Evolution of Processors**

- Transition from current scalar and FPGA approaches to heterogenous processor

- Improve computational performance • Circumvent rigid custom

- SoC limitations

### **DASH Contributors:**

Prof. Ali Akoglu<sup>6</sup> Mr. Greg Ash<sup>5</sup> Prof. David Blaauw<sup>7</sup> Mr. Lee Eisen<sup>2</sup> Mr. Tom Genduso<sup>2</sup> Prof. John Brunhaver<sup>1</sup> Prof. Chaitali Chakrabarti<sup>1</sup> Prof. Ronald Dreslinski<sup>7</sup> Mr. John Fielden<sup>5</sup> Prof. Hun-Seok Kim<sup>7</sup>

Prof. Radu Marculescu<sup>3</sup> Prof. Trevor Mudge<sup>7</sup> Prof. Umit Y. Ogras<sup>1</sup> Dr. Alex Yahja<sup>4</sup> Dr. Bo Ryu<sup>4</sup>

<sup>1</sup>Arizona State University <sup>2</sup>Arm, Ltd. <sup>3</sup>Carnegie Mellon University <sup>4</sup>EpiSci, Inc. <sup>5</sup>General Dynamics Mission Systems <sup>6</sup>University of Arizona <sup>7</sup>University of Michigan

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government.

# **Development of Next Gen Processors**

## Specialized Functions: Domain-specific System-on-Chip (DSSoC)

# Software-Reconfigurable

| Acronym | Definition                                 |

|---------|--------------------------------------------|

| DAP     | Domain Adaptive Processor                  |

| FEC     | Forward Error Correction                   |

| QEMU    | Quick Emulator                             |

| SoC     | System on a Chip                           |

| ASIC    | Application-Specific Integrated<br>Circuit |

## Approach

### Determine Characteristics of SoC

## **Results/Impact**

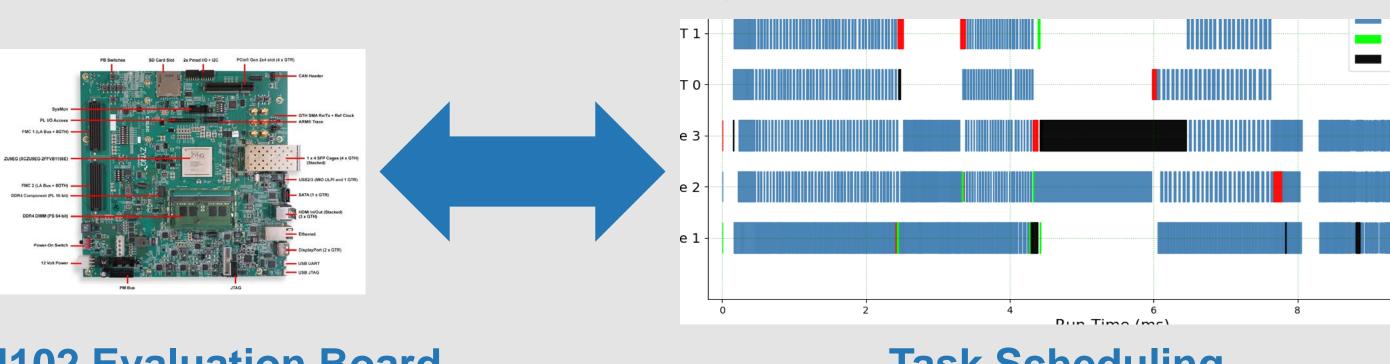

### **ZCU102 Evaluation Board**

Aid implementation by providing software design and testing support for heterogeneous processors

Manage SoC resources with heuristic and learning systems • Demonstrate tools and chip with over-the-air experiments

• Developed high-performance ontological analysis tools - Demonstrated on multiple applications via LLVM extensions

• Automatically mapped algorithms to example chip layouts • Developed QEMU simulation to enable system analysis • Demonstrated preliminary intelligent scheduling on FPGA hardware emulations with hardware accelerations

Implemented multiple example processing elements

**Task Scheduling**

Driving toward detailed hardware specification and performance estimates

• Developing multiple innovative processing elements Energy Efficiency of DAP is 250 GOPs/W and unified FEC is 1 TOPs/W - 70x - 150x better than current general purpose processors (w/o compromising programmability for wireless communications applications)

Contact: Dr. Daniel W. Bliss | d.w.bliss@asu.edu