### **{** Design & Security: Posh Open Source Hardware (POSH)

### Overview

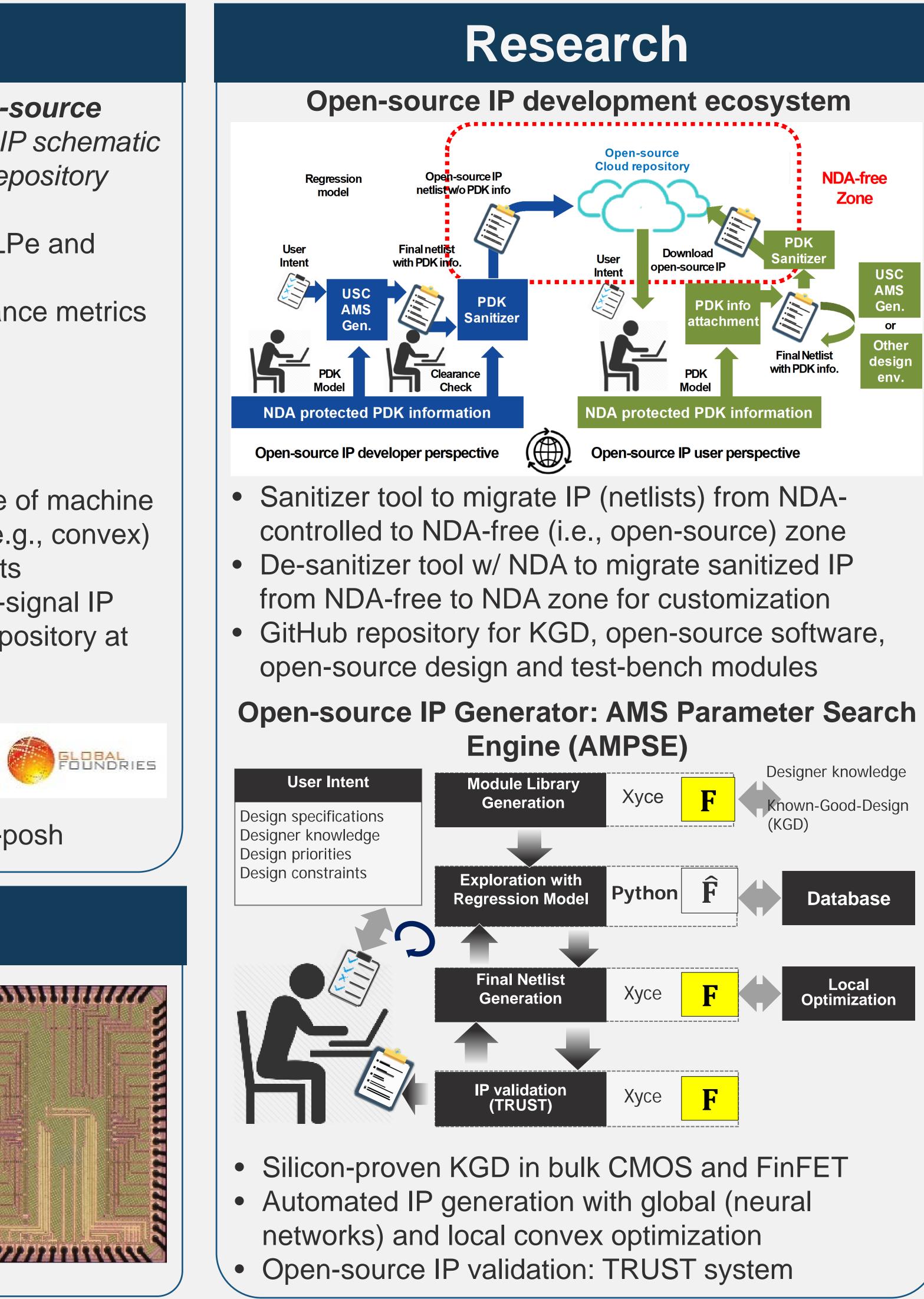

- DARPA-funded ERI POSH TA-2: **Open-source** automated analog mixed-signal (AMS) IP schematic generation and distribution via POSH repository

- Start date June 25, 2018

- Leverage USC circuit designs in GF65LPe and **GF12LP FinFET**

- IP blocks that meet or exceed performance metrics at month 48:

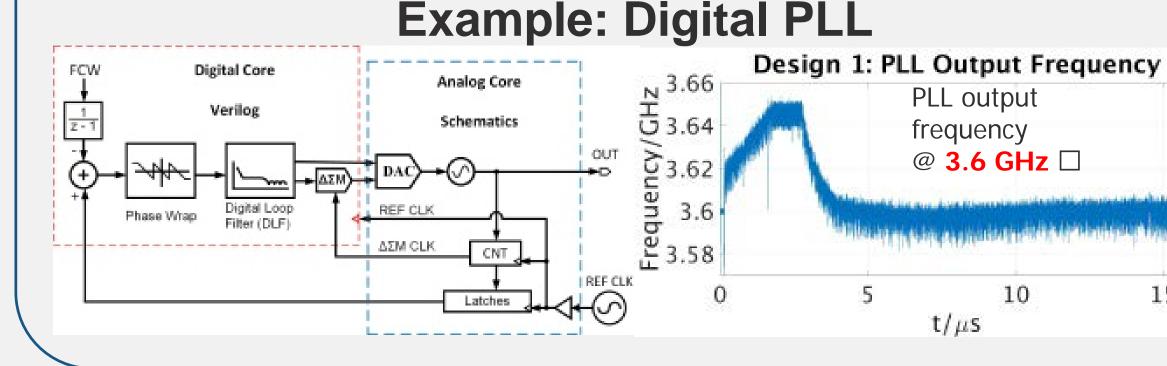

- PLL range: 10 MHz 10 GHz

- DLL range: 10 MHz 10 GHz

- ADC range: 1 10,000 MS/s

- DAC range: 1 10,000 MS/s

- Key aspect of technical approach is use of machine learning (e.g., ANN) and optimization (e.g., convex) around known-good design (KGD) points

- Library of validated open-source mixed-signal IP circuit modules with initial delivery to repository at month 6

- USC\_65nm\_SAR\_ADC\_Dec20\_2018

**USC**University of Southern California

### https://github.com/USCPOSH/usc-posh

### Background

- Previous attempts and lessons learned suggest narrow focused effort around proven known good designs (KGDs) and limited choice of architectures will be most successful approach

- Leverage extensive silicon-proven AMS and optimization experience at USC

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official values or policies of the Department of Defense or the U.S. Government.

# Analog Mixed Signal (AMS) Open-source IP Ecosystem A.F.J. Levi<sup>1</sup>, M.S.W. Chen<sup>1</sup>, S. Gupta<sup>1</sup>, J. Whalen<sup>2</sup>, W. Taylor<sup>3</sup>

USC

Gen.

## Impact

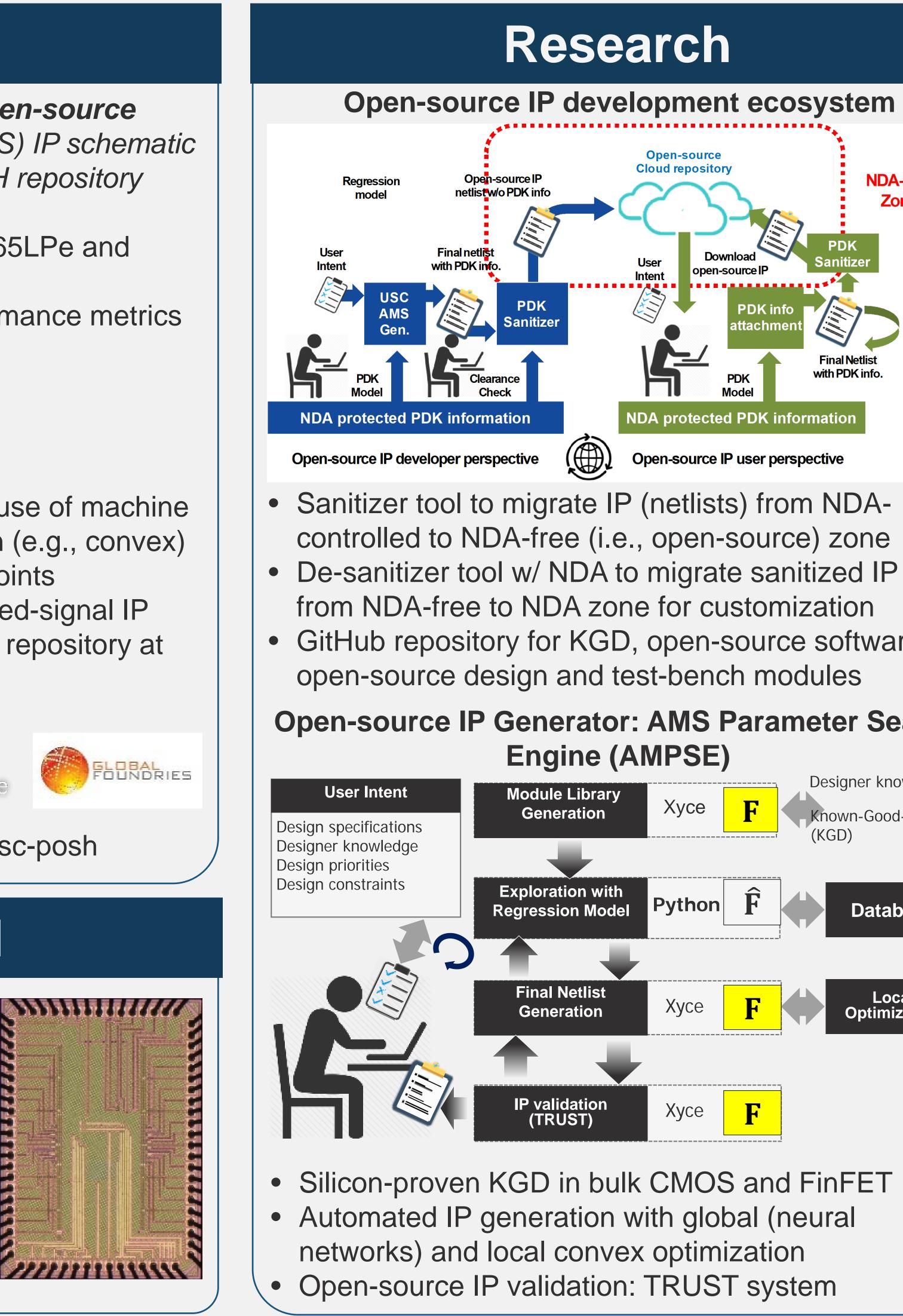

#### Fast circuit module modeling

Neural network based regression model used to characterize parameters-to-metrics mapping of primitive AMS circuit modules. Has sufficient modeling accuracy for appropriate AMS metrics.

#### **Example: bootstrap sampler modeling**

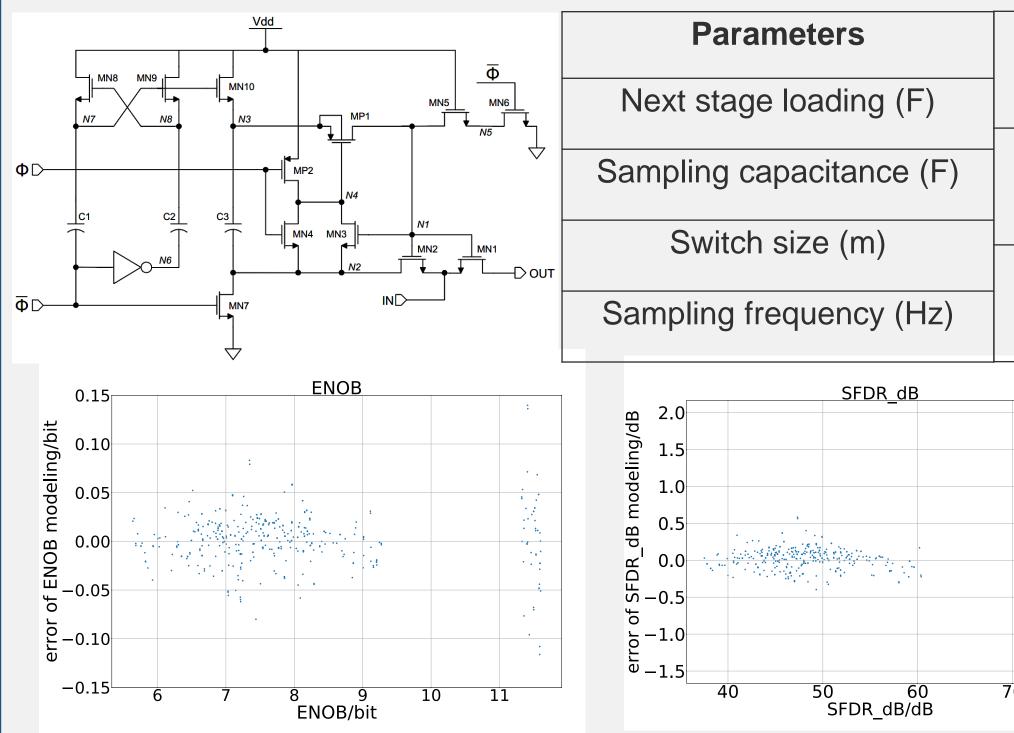

Fast block-level circuit netlist generation

Based on designer's knowledge, block-level specifications are divided into module constraints. In the AMPSE design flow, module-level regression is used to efficiently generate block-level netlists.

### Contact

#### Tony Levi, alevi@usc.edu