# Princeton SDH DECADES Architecture

David Wentzlaff, Princeton University; Margaret Martonosi, Princeton University; Luca Carloni, Columbia University

# Software Defined Hardware (SDH)

# Artificial Intelligence

# Background

## **Target Challenge:** Data Supply is the Fundamental **Bottleneck in Accelerator-Rich Computing Systems**

- Hardware accelerators make data supply bottlenecks dominate runtime

- Key bottlenecks lie in supplying specialized accelerators with data

- Different accelerators and applications have different data supply needs

- Accelerators lack general-purpose latency-tolerance mechanisms

- Accelerator-rich computing requires big increases in memory bandwidth

- Targets machine learning and complex graph applications

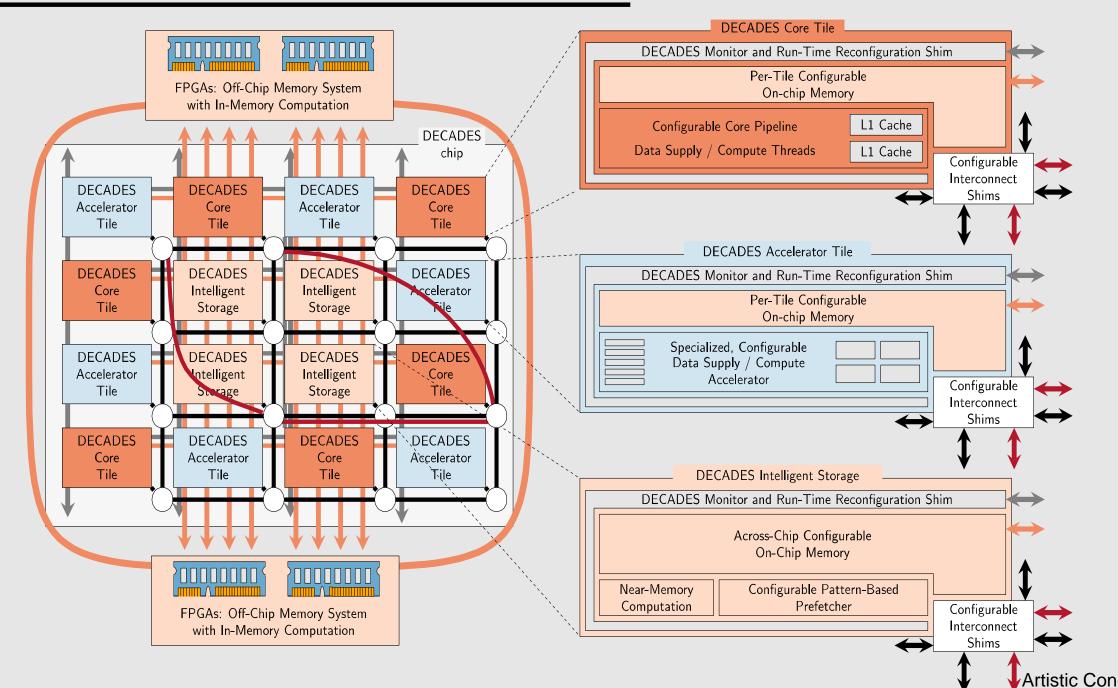

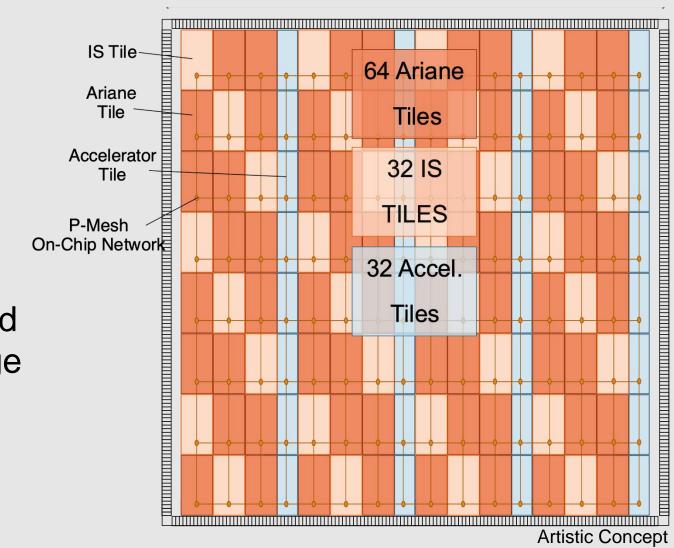

## **DECADES Architectural Overview**

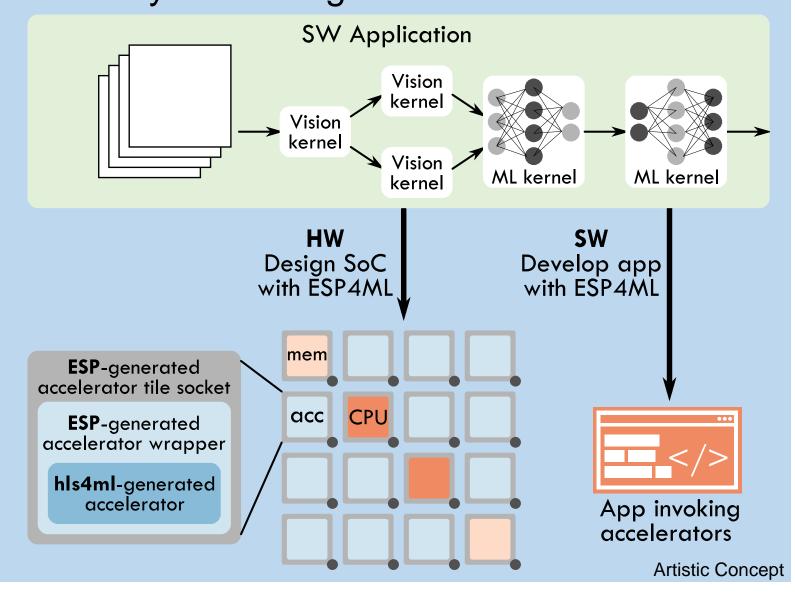

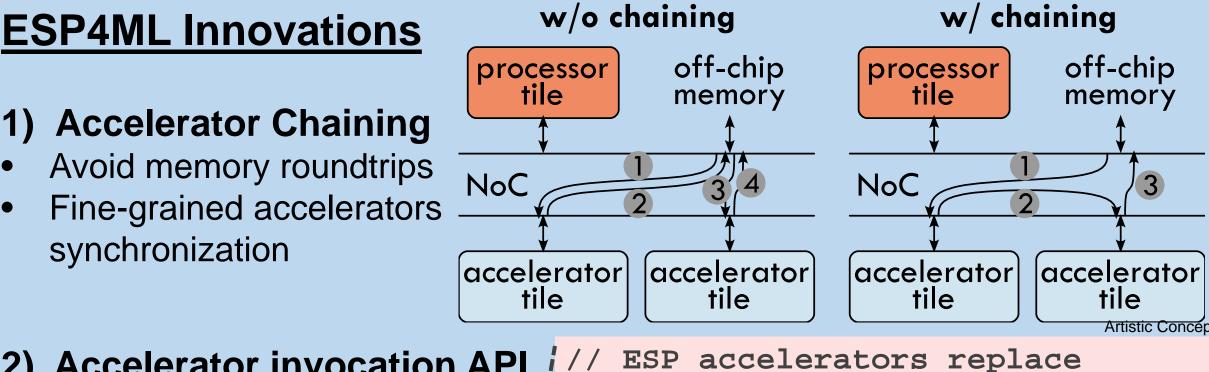

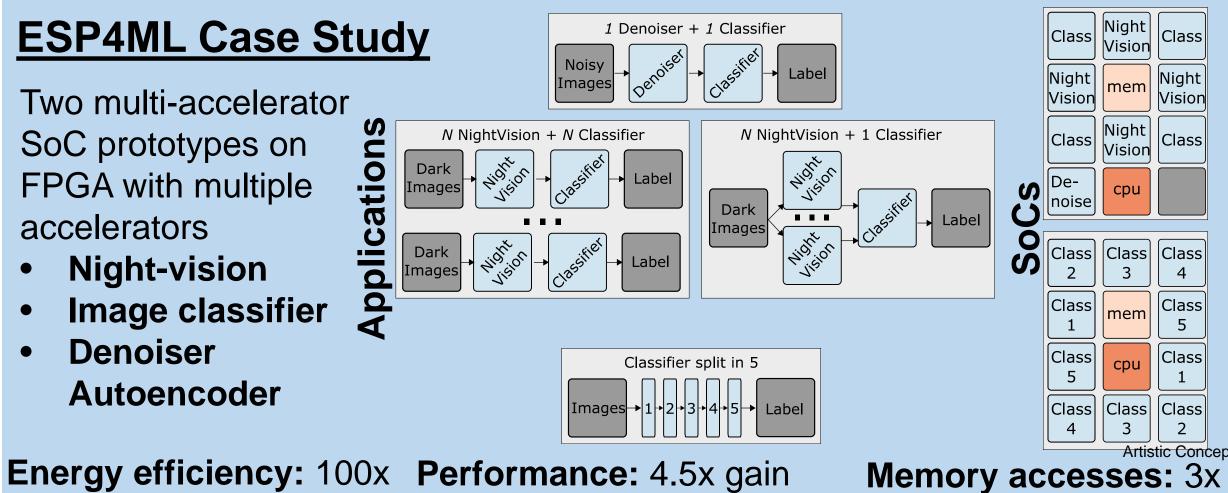

# **ESP4ML (Al accelerator portion of DECADES)** An Open Source Design Flow for Embedded Al Applications

Simplify design and programmability of heterogeneous SoCs for Al

- Generate accelerators from machine learning models given in Keras, Pytorch, ONNX

- Automate accelerator integration in the SoC

- Seamless accelerator programmability from target applications

### Transition Paths: Open-Source Release Contributions

MosaicSim: A cycle-driven, LLVM-based simulator for heterogeneous systems

https://github.com/PrincetonUniversity/MosaicSim

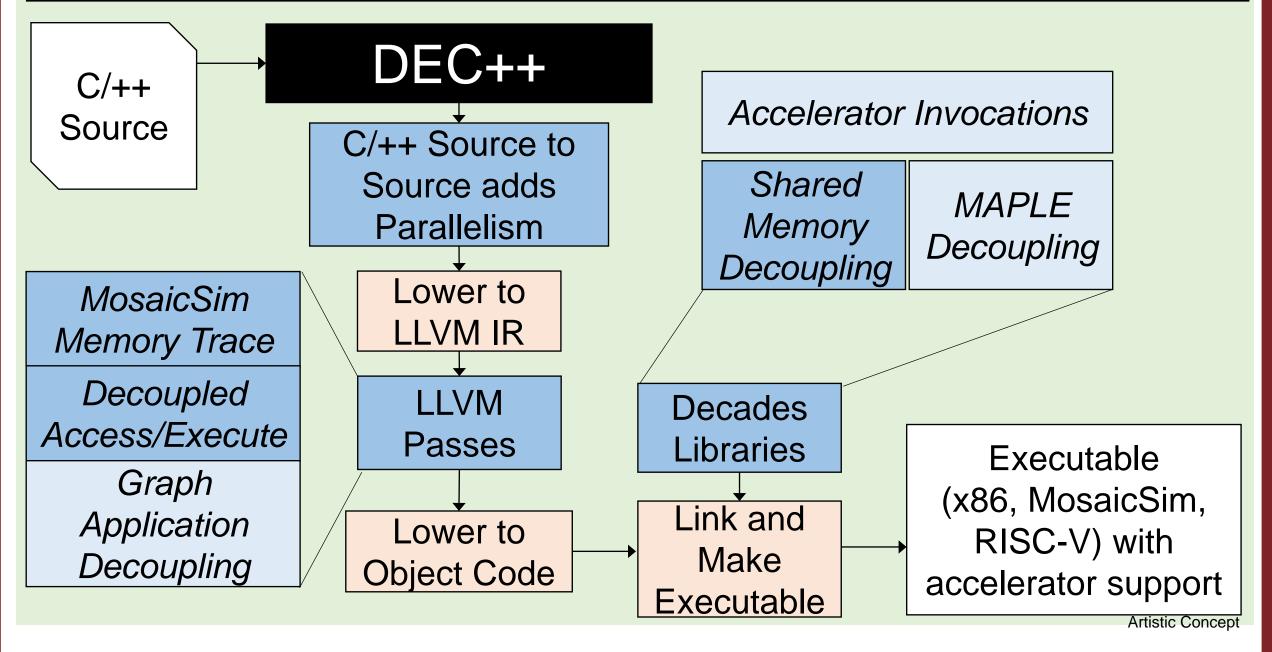

**DEC++**: LLVM-based compiler and runtime; supports C/++, and Python

https://github.com/PrincetonUniversity/DecadesCompiler

MosaicSim and DEC++ Support: Docker/Documentation/Tutorial

- https://hub.docker.com/repository/docker/princetondecades/decades

- https://github.com/amanocha/DECADES\_Applications

**OpenPiton**: General purpose, multithreaded manycore RISC-V processor

https://github.com/PrincetonUniversity/openpiton

https://github.com/sld-columbia/esp

**ESP**: Open-source research platform for heterogeneous SoC design

# Approach

**DECADES** is a Vertically-Integrated Software/Hardware approach that combines Language and Compiler support to map complex graph and Machine Learning applications to a novel, heterogeneous, accelerator-rich manycore architectures.

## **DECADES Key Innovations:**

- Intelligent Storage tiles orchestrate on-chip data movement between accelerators and accelerators, accelerators and core, and core to core

- Best-of-breed pluggable accelerator socket and High-Level Synthesis flow ease accelerator integration (ESP and ESP4ML)

- Rich compiler (DEC++) and language infrastructure automatically slices applications and maps graph applications onto accelerators and cores

- DECADES architecture contains both near memory and in-memory computation to reduce energy of data movement (ComputeDRAM)

- Strong commitment to open source release of software and hardware

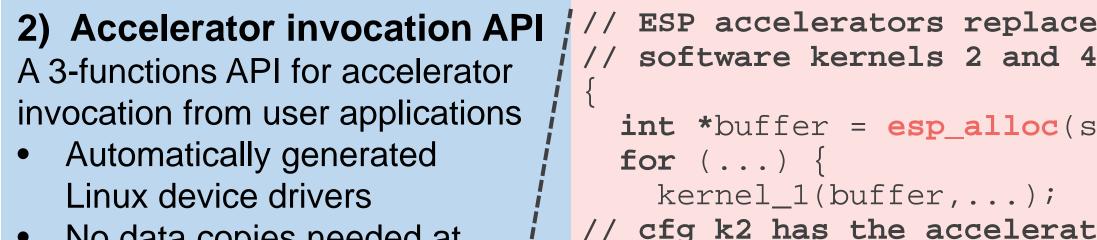

## **DECADES DEC++ Compiler and Accelerator Invocation Flow**

**ESP Library**

mode

kernel

int \*buffer = esp\_alloc(size); for (...) kernel\_1(buffer,...); // cfg\_k2 has the accelerator configuration parameters esp\_run(buffer, cfg\_k2); kernel\_3(buffer,...); esp\_run(buffer, cfg\_k4); esp\_free(buffer); **ESP** accelerator driver

**Artistic Concept**

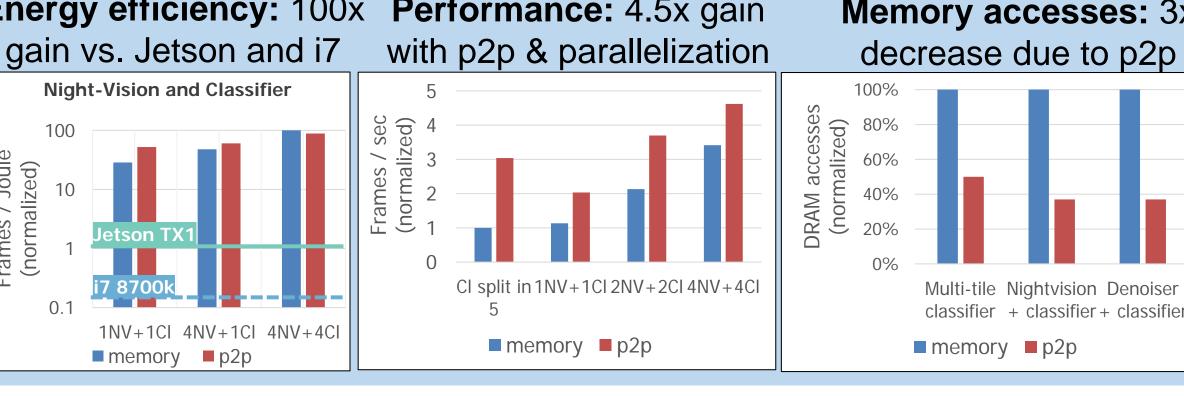

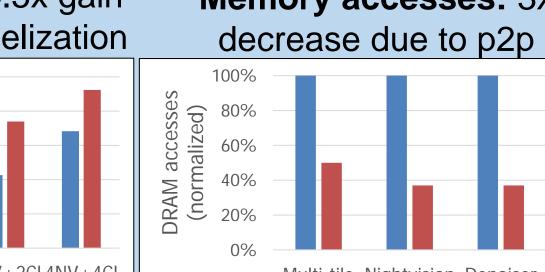

memory p2p

# Results and Impact

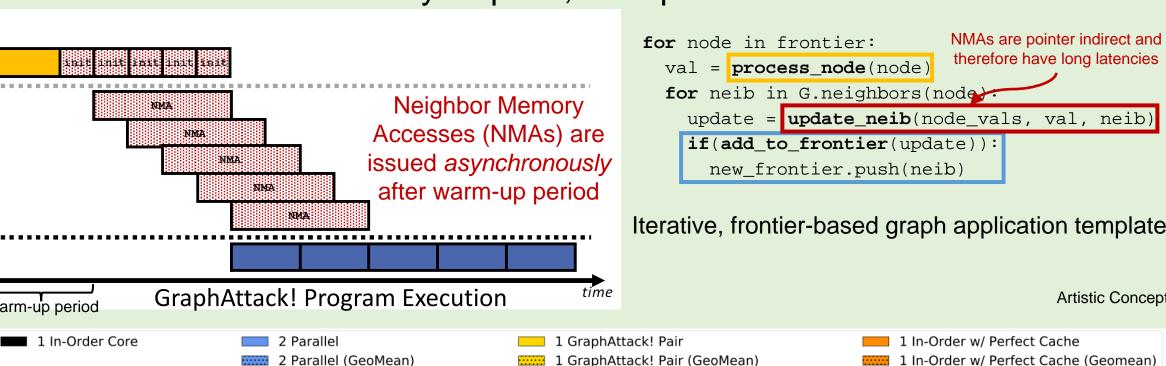

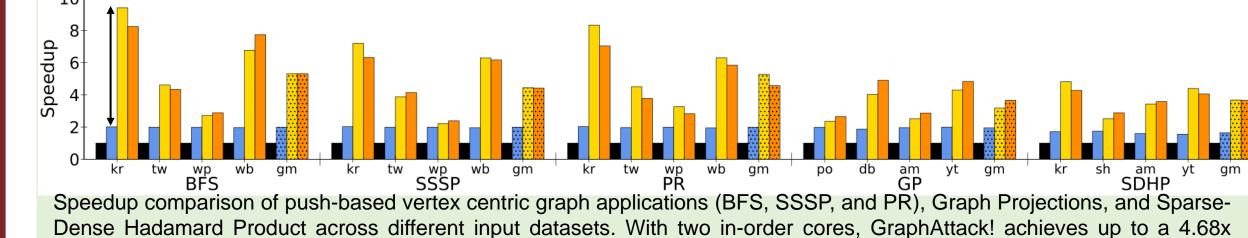

GraphAttack!: HW/SW co-design to hide long latencies of indirect Neighbor Memory Accesses (NMAs) that bottleneck graph applications

- DEC++ Producer/Consumer program slicing where Producer issues NMAs and Consumer performs computation with their data

- Intelligent Storage Tile asynchronously performs NMAs

- Producer issues memory request; data provided to Consumer

speedup (geomean 2.48x) over traditional do-all parallelism and can outperform an in-order core with a perfect cache

# **DECADES Testchip 1**

- Enables testing hardware and software innovation

- Over 100 tiles

- Core Tiles (cache coherent)

- RISC-V 64-bit Ariane Intelligent Storage Tiles

- Programmatically controlled data movement and storage

- Accelerator Tiles

- Specialized hardware

- Over 1B transistors

- 1.5GHz target frequency

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government. Distribution Statement A – Approved for Public Release, Distribution Unlimited