### Background

Ever-Demanding Computing Power for AI and Machine-Learning Workloads

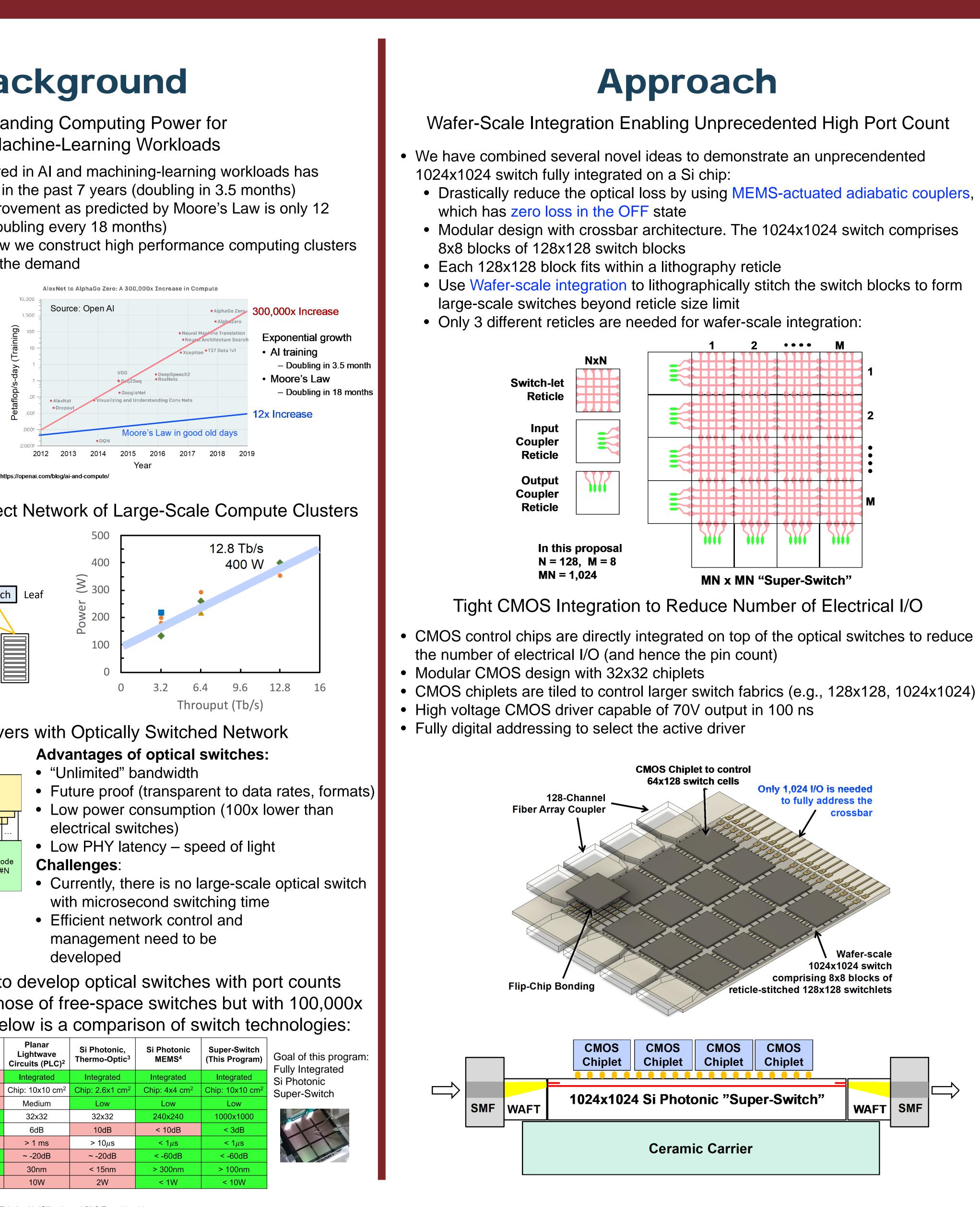

- The computing power required in AI and machining-learning workloads has increased by 300,000 times in the past 7 years (doubling in 3.5 months)

- However, the hardware improvement as predicted by Moore's Law is only 12 times in the same period (doubling every 18 months)

- Fundamental changes in how we construct high performance computing clusters are needed to keep up with the demand

- Traditional electrically switched networks are facing fundamental limits in power consumption

PIPES

- For example, commercial switch chips with 12.8 Tb/s throughput consumes 400W

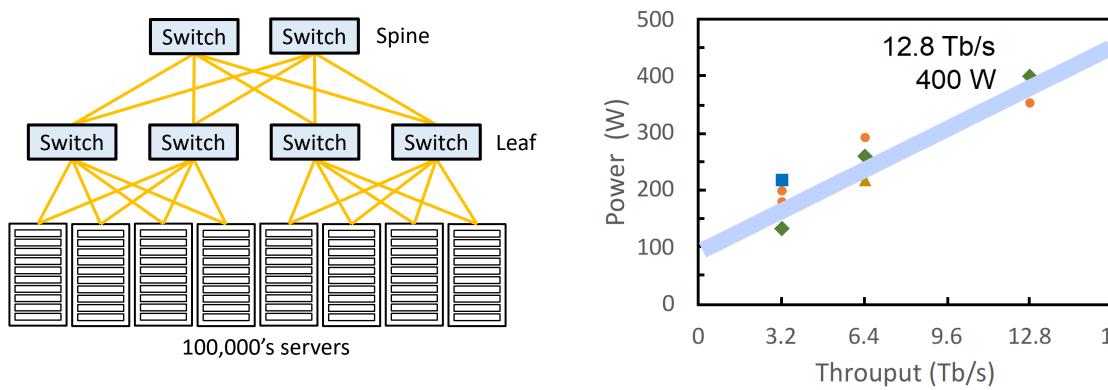

- Optically switched network could enable much larger cluster HPC

"Power Wall" in Interconnect Network of Large-Scale Compute Clusters

#### Scaling of AI Servers with Optically Switched Network

Goal of this research is to develop optical switches with port counts approaching (exceeding) those of free-space switches but with 100,000x faster switching speed. Below is a comparison of switch technologies:

| Commercial<br>3D MEMS-based<br>Free-Space<br>Switches                                   | Switch Type  | 3D MEMS <sup>1</sup>       | Planar<br>Lightwave<br>Circuits (PLC) <sup>2</sup> | Si Photonic,<br>Thermo-Optic <sup>3</sup> | Si Photonic<br>MEMS <sup>4</sup> | Super-Switch<br>(This Program) | Goal of<br>Fully Inte<br>Si Photo<br>Super-S |

|-----------------------------------------------------------------------------------------|--------------|----------------------------|----------------------------------------------------|-------------------------------------------|----------------------------------|--------------------------------|----------------------------------------------|

|                                                                                         | Construction | Free Space                 | Integrated                                         | Integrated                                | Integrated                       | Integrated                     |                                              |

|                                                                                         | Size         | ~ 30x45x50 cm <sup>3</sup> | Chip: 10x10 cm <sup>2</sup>                        | Chip: 2.6x1 cm <sup>2</sup>               | Chip: 4x4 cm <sup>2</sup>        | Chip: 10x10 cm <sup>2</sup>    |                                              |

|                                                                                         | Cost         | High                       | Medium                                             | Low                                       | Low                              | Low                            |                                              |

|                                                                                         | Port Count   | 320x320                    | 32x32                                              | 32x32                                     | 240x240                          | 1000x1000                      |                                              |

|                                                                                         | Optical Loss | < 3dB                      | 6dB                                                | 10dB                                      | < 10dB                           | < 3dB                          |                                              |

|                                                                                         | Switch Time  | 25 ms                      | > 1 ms                                             | > 10µs                                    | < 1µs                            | < 1µs                          |                                              |

|                                                                                         | Crosstalk    | < -65dB                    | ~ -20dB                                            | ~ -20dB                                   | < -60dB                          | < -60dB                        |                                              |

| [Calient Inc.] R. Helkey <i>et al.</i><br><i>Optics &amp; Photonics News</i> , May 2002 | Bandwidth    | > 500nm                    | 30nm                                               | < 15nm                                    | > 300nm                          | > 100nm                        |                                              |

|                                                                                         | Power Consp  | 50W                        | 10W                                                | 2W                                        | < 1W                             | < 10W                          |                                              |

Calient S320 switch, http://www.calient.ne

K. Suzuki et al., "Low-Insertion-Loss and Power-Efficient 32 × 32 Silicon Photonics Switch With Extremely

# **Silicon Photonic Super-Switch** Ming C. Wu (PI), Vladimir Stojanovic, and Eli Yablonovitch, UC Berkeley Paraskevas Bakopoulos, Elad Mentovich, Mellanox

This research was developed with funding from the Defense Advanced Research Projects Agency (DARPA). The views, opinions and/or findings expressed are those of the author and should not be interpreted as representing the official views or policies of the Department of Defense or the U.S. Government. Distribution Statement A – Approved for Public Release, Distribution Unlimited

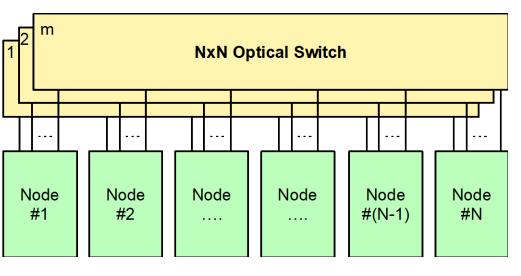

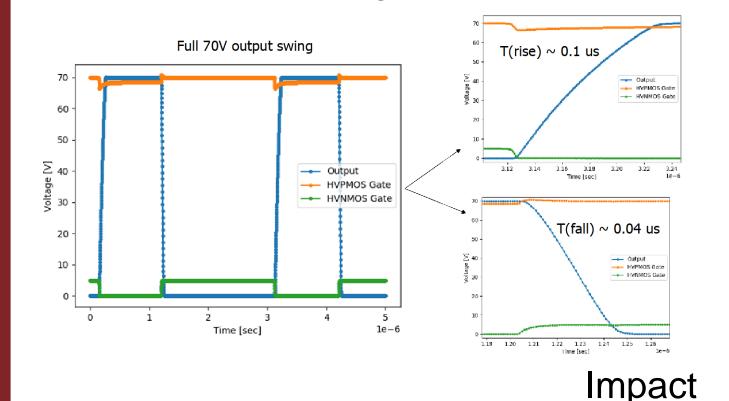

## Heterogeneous 3D

## **Results and Impact**

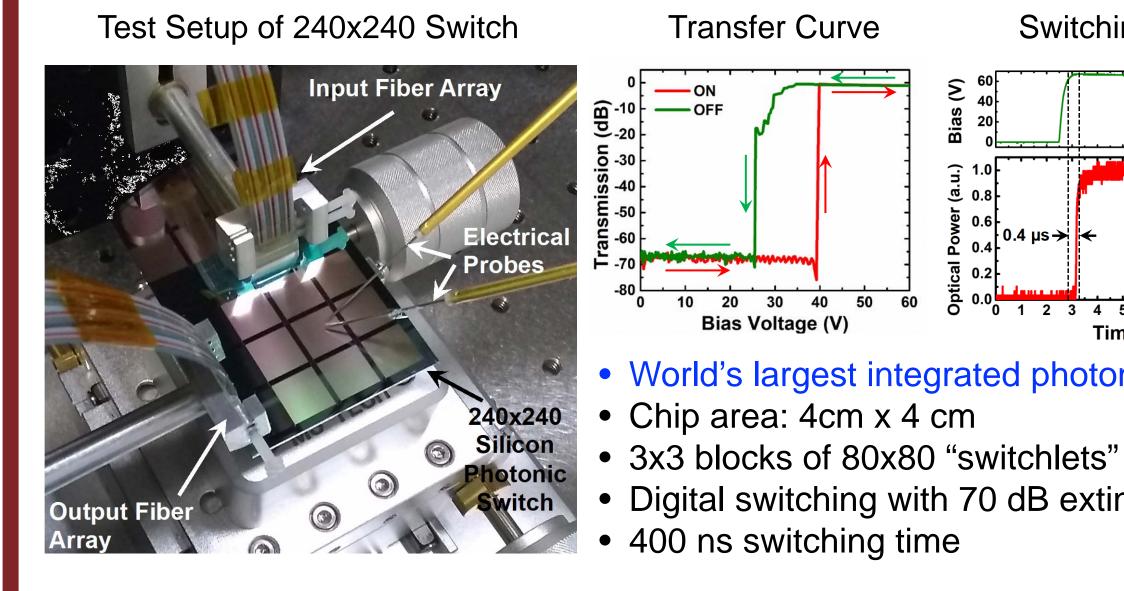

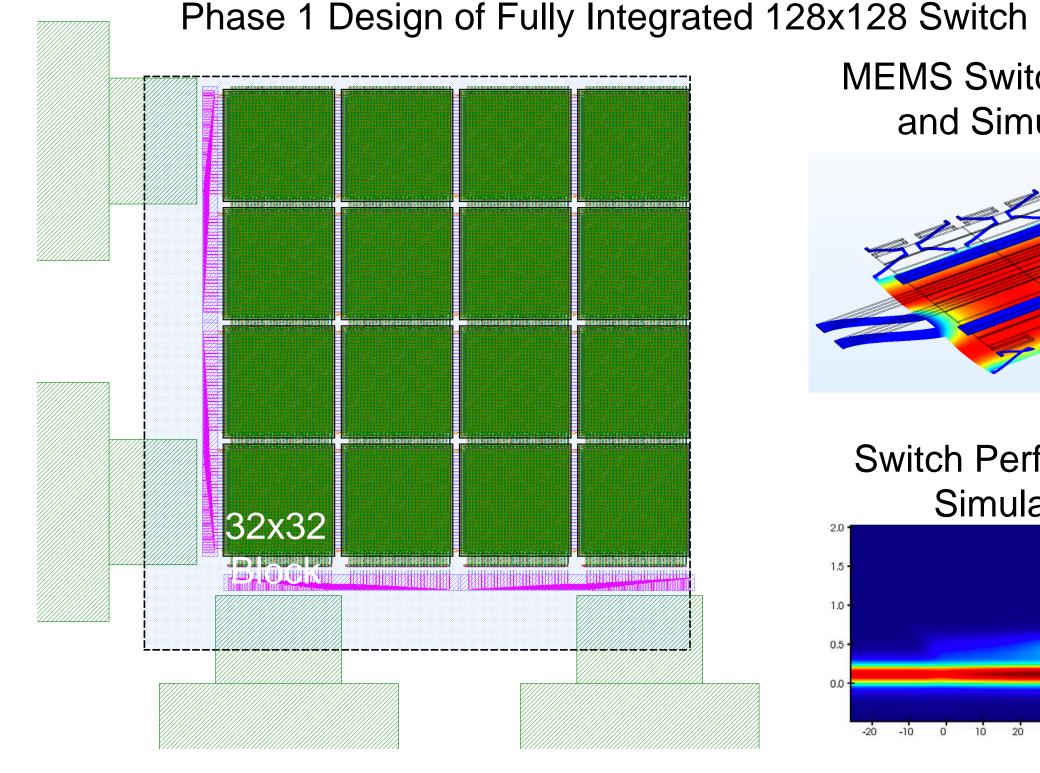

Wafer-Scale Integrated 240x240 switches

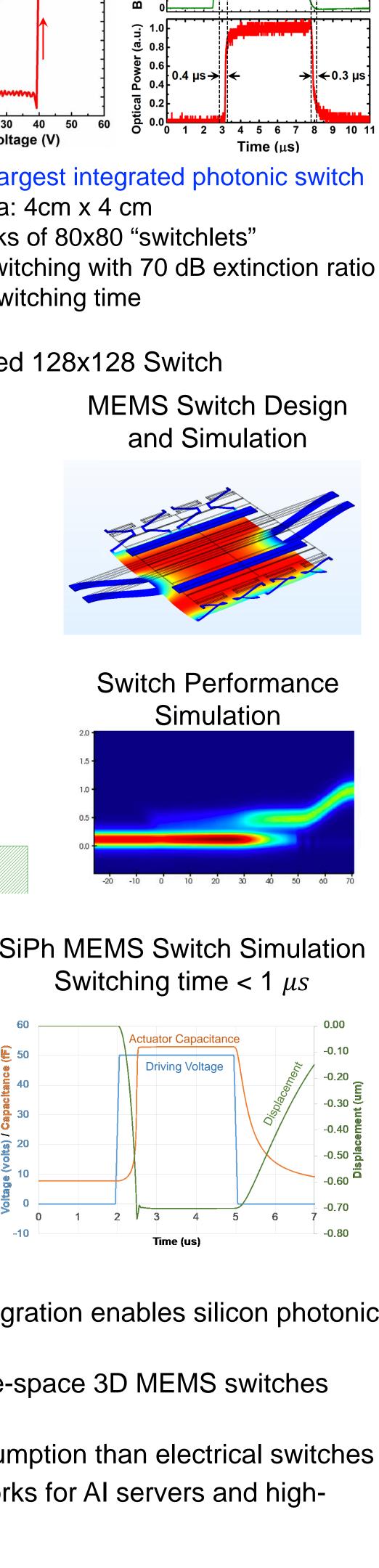

CMOS Design and Simulation 70V Swing in 100 ns

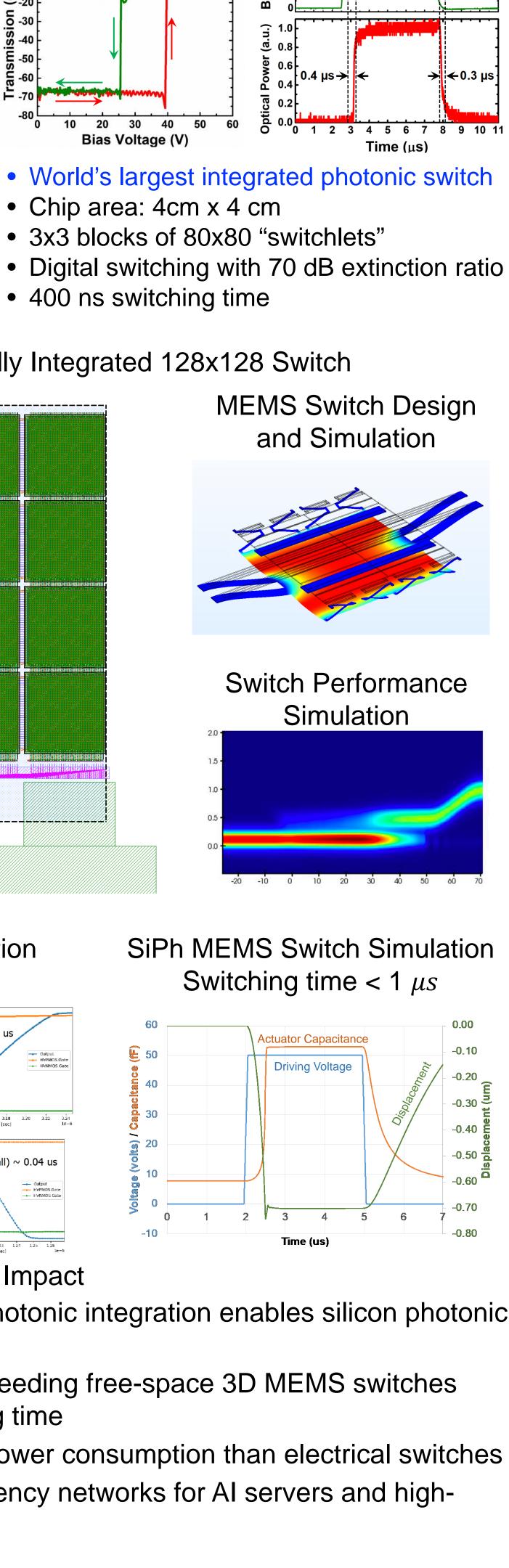

- Novel wafer-scale electronic-photonic integration enables silicon photonic switches with

- Port counts approaching/exceeding free-space 3D MEMS switches but 100,000x faster switching time

- Orders of magnitude lower power consumption than electrical switches

- Enable high bandwidth, low latency networks for AI servers and highperformance computers (HPC)

Switching Time

<sup>5.</sup> Sohma, T. Watanabe, N. Ooba, M. Itoh, T. Shibata, and H. Takahashi, "Silica-based PLC Type 32 x 32 Optical Matrix Switch," ECOC 2006

High-Δ Silica PLC Connector," J. Lightwave Technol., JLT, vol. 37, no. 1, pp. 116–122, Jan. 2019. T. J. Seok, K. Kwon, J. Henriksson, J. Luo, and M. C. Wu, "Wafer-scale silicon photonic switches bevond die size limit," Optica, vol. 6, no. 4, pp. 490–494, Apr. 2019