# SERGEY SHUMARAYEV

**DISTINGUISHED ARCHITECT**INTEL PSG CTO OFFICE

The views and conclusions contained in this document are those of the authors and should not be interpreted as representing the official policies, either expressed or implied, of the U.S. Government.

### SYNCHRONIZED CO-ARCHITECTURE IS ESSENTIAL

"It may prove to be more economical to build large systems out of smaller functions, which are separately packaged and interconnected<sup>1</sup>."

Gordon E. Moore

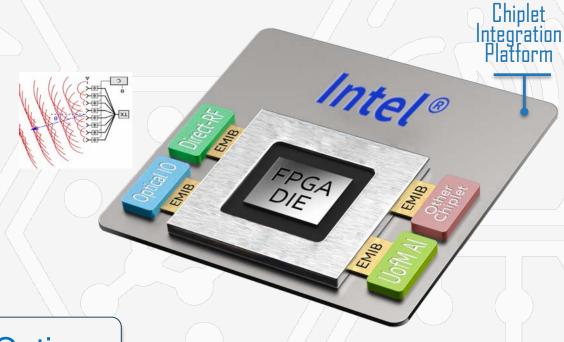

Connect chips and chiplets in a package to match or exceed the functionality of a monolithic SOC

High density, low cost interconnect with high bandwidth at low power is essential

## **INNOVATION WITH PARTNERS**

**CHIPLET LIBRARY ADVANCED PACKAGING TECHNOLOGY** ADC/DAC **FPGA Machine Learning** Analog ASIC Front End Memory 0 nm AIB **FPGA Processors** Cores **FPGA** Cores **Adjacent IP** Crypto = Accelerator ...Your Ideas Advanced Interface Accelerator Comms Bus (AIB) = AIB Interface Flip-Chip Microbump DIE 2 DIE 1 DIE 3 Pitch pitch 55um > 100um Intel® Embedded Multi-Die Interconnect Bridge (EMIB)

Platform for innovation through ecosystem

Explore new business models

Serking teratement of partiners hips

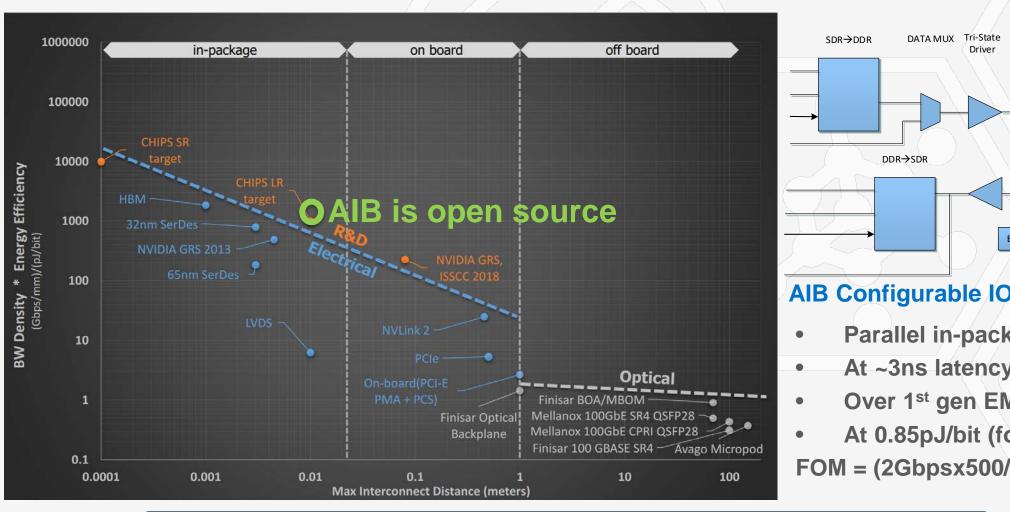

## CHIPS: FOM & INTERFACE

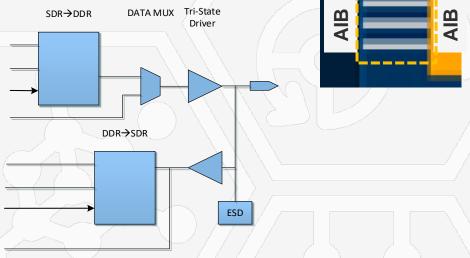

#### **AIB Configurable IO Cell**

- Parallel in-package (2Gbps/IO)

- At ~3ns latency

- Over 1st gen EMIB (500 IOs/mm)

- At 0.85pJ/bit (for 55um ubump)

FOM = (2Gbpsx500/mm)/(0.85pJ/bit) = 1176

Heterogeneous Integration with SoC-like performance

DISTRIBUTION STATEMENT A. Approved for public release

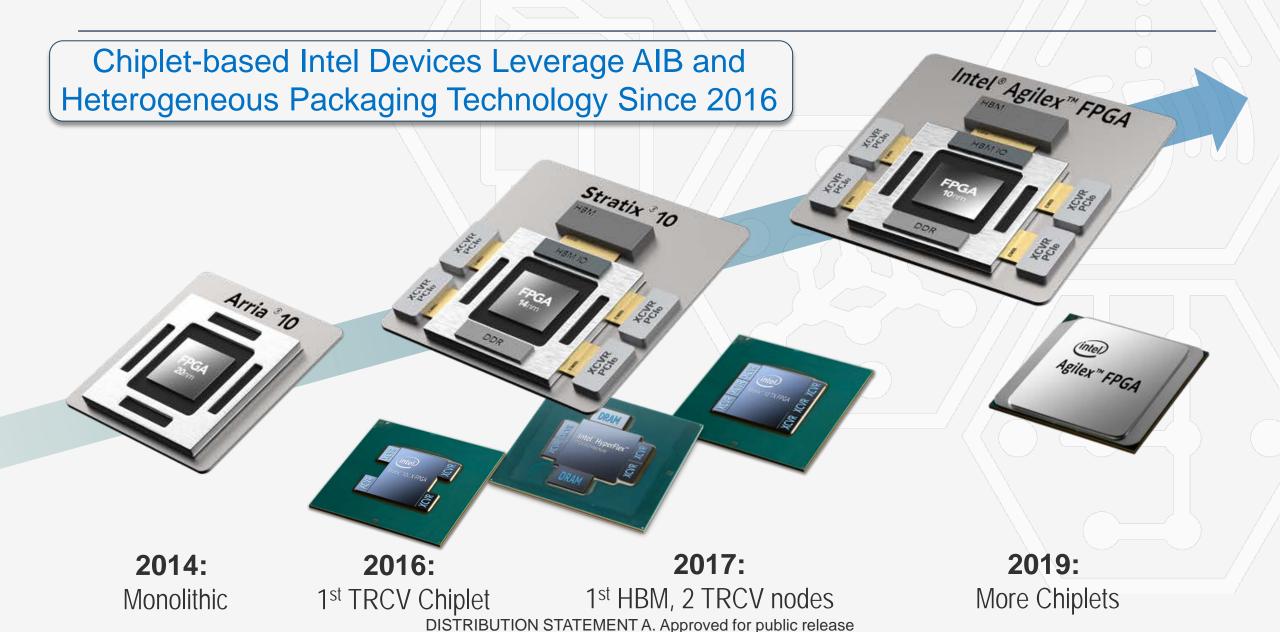

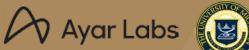

## INTEL® FPGA EVOLUTION: HETEROGENEOUS IS HERE

## INNOVATION VIA INTEGRATION: PARTNERSHIP

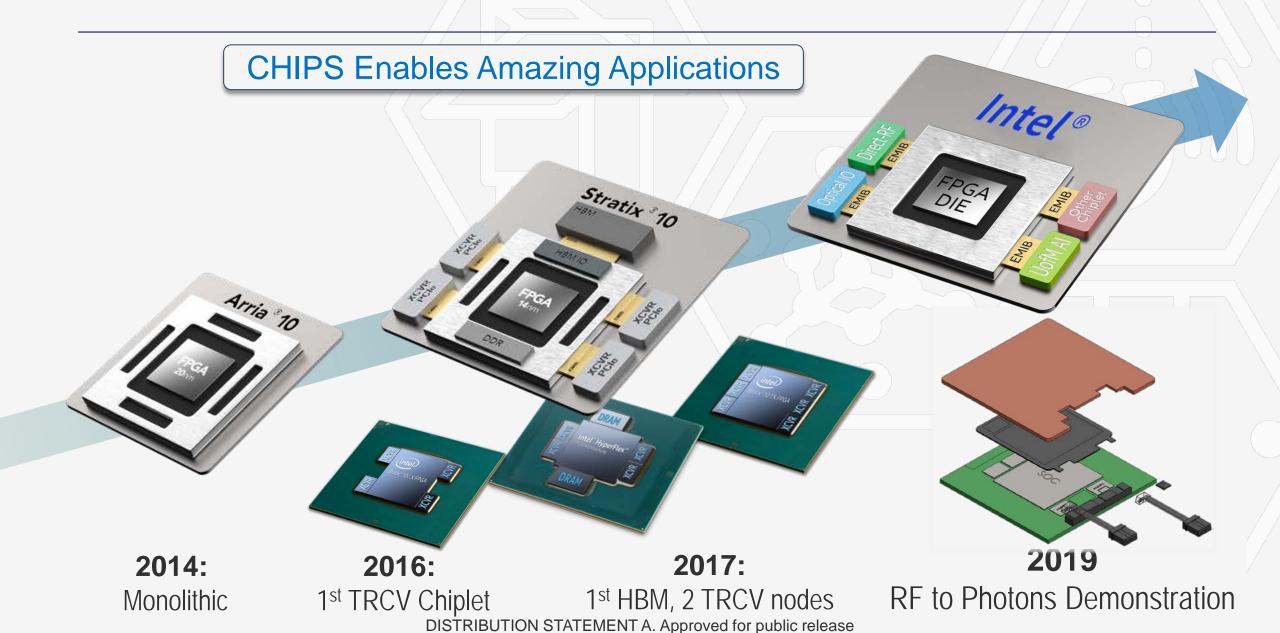

## **CHIPS:** REVOLUTIONARY SYSTEM INTEGRATION

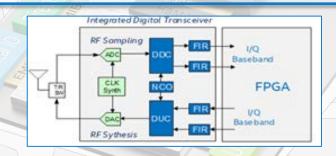

## Direct-RF

**CHIPS Enables Amazing Applications**

Uncompromised RF performance (GOMAC 2019)

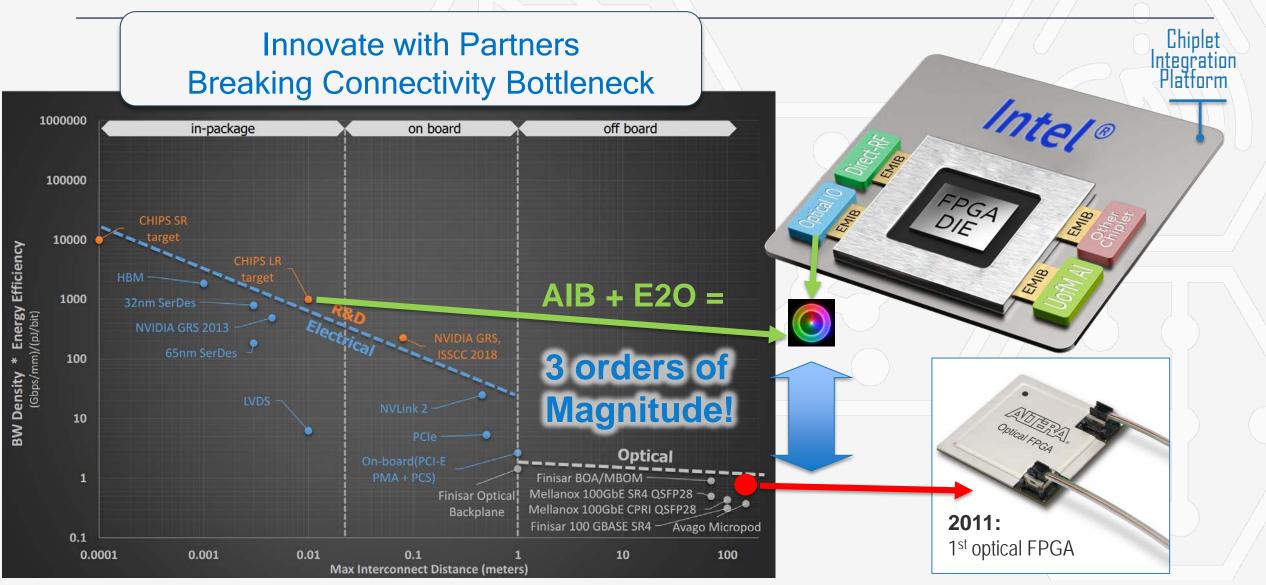

## Optical 10

Breaking connectivity bottleneck (HOTCHIPS 2019)

## Research Platform

Research at commercial level **UofM AI Chiplet**

Chiplet-Based Architecture

Library of chiplets: XCVR, custom I/O & compute tiles

## CHIPS: APPLICATION TO WIRELESS SYSTEMS

- Systems Trending Towards All Digital

- Data Converters at Every Antenna

- Size, Weight and Power

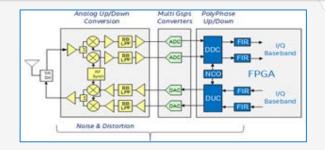

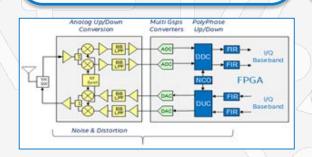

**RF Integration Options**

On Board (Discrete Analog Devices Connected via JESD) Monolithic (Traditional SoC)

Chiplet (Chiplet Integration\_ Platform, i.e. CHIPS)

## CHIPS: DIRECT-RF CHIPLET BENEFITS

On Board: (Discrete Analog Devices Connected via JESD) Monolithic (Traditional SoC)

Chiplet (Chiplet Integration Platform, i.e. CHIPS)

| Parameter                  | Benefits of Chiplet Approach vs. Alternatives                    |

|----------------------------|------------------------------------------------------------------|

| Sample Rate: Up to 64 GSPs | ~6x and higher sample rates, superior performance over higher BW |

| IBW: >25GHz                | 8x higher bandwidth                                              |

| IF Stage                   | Not required, reducing SWAP, Improved system NF                  |

| JESD                       | No JESD Required, Reducing power                                 |

Opportunities to Improve Size, Weight and Power with Partner Innovation

## CHIPS: OPTICAL IO CHIPLET BENEFITS Ayar Labs

### **SUMMARY**

#### The Time for Chiplets Is Now

- Chiplets needed to drive joint innovation

- We have the technology

- Chiplet-based Intel Stratix 10 devices shipping since 2016

## Significant Chiplet Milestones This Year

- Optical + DirectRF + University Research

- 2<sup>nd</sup> chiplet-based family (Intel Agilex FPGAs) begins shipping

#### Join the Growing Chiplet Ecosystem

- Your chipet here!

- How can you leverage 1Tb/s of BW?

Start here for more information, specifications, and more: https://intel.ly/2LISZcr

## **ACKNOWLEDGMENT**

The author would like to thank **Dr. William Chappell**, **Dr. Dan Green**, **Mr. Andreas Olofsson** and **Dr. Gordon Keeler** for their support.

## **LEGAL NOTICES & DISCLAIMERS**

INTEL CORPORATION LEGAL DISCLAIMER: Tests document performance of components on a particular test, in specific systems. Differences in hardware, software, or configuration will affect actual performance. Consult other sources of information to evaluate performance as you consider your purchase. For more complete information about performance and benchmark results, visit www.intel.com/benchmarks. Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at www.intel.com, or from the OEM or retailer. Software and workloads used in performance tests may be optimized for performance only on Intel microprocessors. Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information, visit www.intel.com/performance. Results have been estimated based on internal Intel analysis and are provided for informational purposes only. Any difference in system hardware or software design or configuration may affect actual performance. Cost reduction scenarios described are intended as examples of how a given Intel-based product, in the specified circumstances and configurations, may affect future costs and provide cost savings. Circumstances will vary. Intel does not guarantee any costs or cost reduction. This document contains information on products, services and/or processes in development. All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest forecast, schedule, specifications and roadmaps.